# INCREMENTAL PLACEMENT FOR FIELD-PROGRAMMABLE GATE ARRAYS

by

## David Leong

B.A.Sc., University of British Columbia, 2004

# A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

MASTER OF APPLIED SCIENCE

in

THE FACULTY OF GRADUATE STUDIES

(Electrical and Computer Engineering)

#### UNIVERSITY OF BRITISH COLUMBIA

November, 2006

© David Leong, 2006

## **Abstract**

As the logic capacity of FPGAs continues to increase with deep submicron technology, performing a full recompilation for small iterative changes in a large design is an extremely time-consuming and costly process. To address this issue, this thesis presents a new incremental placement algorithm for FPGAs named "iPlace" that significantly reduces the time required for recompilation. The iPlace algorithm is based on shifting, compaction, and annealing. Key ideas from the algorithm include a placement super-grid that is larger than the physical size of the FPGA. The super-grid allows insertion of additional CLBs into areas with no free locations by CPU-efficient shifting. This is followed by a compaction scheme to re-legalize CLBs that are shifted to illegal locations outside of the physical size of the FPGA. The algorithm ends with a low-temperature anneal to improve quality. This algorithm is capable of handling multiple design changes across large regions of a FPGA. This is especially useful for hierarchical designs where sub-circuits are re-used multiple times. If one such sub-circuit is modified, iPlace can quickly produce a high quality incremental placement solution. For a single region of design change, we found that iPlace is 34 to 260 times faster than the academic tool Versatile Place and Route (VPR) in default mode. Compared to VPR's reduced-quality "-fast" placement option, iPlace is 3 to 28 times faster with equivalent quality. For multiple regions of design changes, iPlace is still 50-70 times faster compared to VPR in default mode when up to 2/3 of the CLBs are modified. Compared to the "-fast" placement option, iPlace is still 5-8 times faster. We believe that iPlace is the first academically available incremental placement algorithm capable of handling significant changes to a netlist for very large circuits.

## **Table of Contents**

| Ab  | ostract                                                                                                                                                                                | ii                        |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| Tab | ble of Contents                                                                                                                                                                        | iii                       |

| Lis | st of Tables                                                                                                                                                                           | V                         |

| Lis | st of Figures                                                                                                                                                                          | viii                      |

| Glo | ossary                                                                                                                                                                                 | x                         |

| Ac  | cknowledgements                                                                                                                                                                        | xi                        |

| De  | edication                                                                                                                                                                              | xii                       |

| 1.  | Introduction                                                                                                                                                                           | 2                         |

| 2.  | 2.1. FPGA Architecture 2.2. FPGA CAD Flow 2.2.1. Technology Mapping 2.2.2. Clustering 2.2.3. Placement 2.2.4. Routing                                                                  | 5<br>10<br>11<br>12<br>13 |

|     | 2.3. Incremental Placement Techniques  2.4. Fast Placement Techniques                                                                                                                  |                           |

| 3.  | 3.1. Initial placement 3.2. Floor-planning 3.3. Expansion 3.4. Compaction. 3.5. Refinement 3.6. Additional Tuning Considerations 3.7. Algorithm Conclusions 3.8. Algorithm Limitations |                           |

| 4.  | Results 4.1. Experimental Goals 4.2. Experimental Baseline 4.3. Single-Region Synthetic Benchmarks 4.3.1. Benchmark Formulation 4.3.2. Runtime Results 4.3.3. Channel Width Results    |                           |

|     | 4.3.4.       | Critical Path Results                                 | 53  |

|-----|--------------|-------------------------------------------------------|-----|

|     | 4.3.5.       | Placement Stability Results                           |     |

|     | 4.3.6.       | Conclusions for Synthetic Benchmarks                  | 55  |

|     | 4.4. Single  | -Region Re-synthesis Benchmarks                       | 56  |

|     | 4.4.1.       | Benchmark Formulation                                 | 56  |

|     | 4.4.2.       | Runtime Results                                       | 57  |

|     | 4.4.3.       | Channel Width Results                                 | 59  |

|     | 4.4.4.       | Critical Path Results                                 | 60  |

|     | 4.4.5.       | Placement Stability Results                           | 61  |

|     | 4.4.6.       | Conclusions for Single-Region Re-synthesis Benchmarks | 62  |

|     | 4.5. Multi-  | Region Re-synthesis Benchmarks                        |     |

|     | 4.5.1.       | Benchmark Formulation                                 |     |

|     | 4.5.2.       | Runtime Results                                       | 65  |

|     | 4.5.3.       | Channel Width Results                                 | 66  |

|     | 4.5.4.       | Critical Path Results                                 | 67  |

|     | 4.5.5.       | Conclusions for Multi-Region Re-synthesis Benchmarks  |     |

|     | 4.6. Experi  | mental Conclusions                                    | 69  |

|     | -            |                                                       |     |

| 5.  | Qualitative  | comparisons                                           | 72  |

| 6.  | Conclusion   | ns and Future Work                                    | 74  |

|     | 6.1. Future  | work                                                  | 76  |

|     | 6.1.1.       | Support for Macro Blocks                              | 76  |

|     | 6.1.2.       | Support for Carry Chains                              | 76  |

|     | 6.1.3.       | Smart Shifting                                        | 77  |

|     | 6.1.4.       | Analytical Placement Refinement Stage                 | 77  |

|     | 6.1.5.       | Integration with Commercial tools                     | 77  |

|     | 6.1.6.       | Incremental Routing                                   | 78  |

| BIF | BLIOGRAP     | HY                                                    | 79  |

|     | 2210 014 11  |                                                       |     |

| Ap  | pendix A: Si | ngle-Region Synthetic Benchmark Results               | 84  |

| Ap  | pendix B: Si | ingle-Region Physical Re-Synthesis Benchmark Results  | 103 |

| Ap  | pendix C: M  | Sulti-Region Physical Re-Synthesis Benchmark Results  | 107 |

## **List of Tables**

| Table 1 Altera Stratix Family of FPGAs                                                     | 9    |

|--------------------------------------------------------------------------------------------|------|

| Table 2 Synthetic 2.5 Benchmark Characteristics                                            | . 48 |

| Table 3 Synthetic 5 Benchmark Characteristics                                              | . 49 |

| Table 4 Synthetic 10 Benchmark Characteristics                                             | . 49 |

| Table 5 Synthetic 2.5d Benchmark Characteristics                                           | . 49 |

| Table 6 Synthetic 5d Benchmark Characteristics                                             | . 49 |

| Table 7 Runtime Speedup of iPlace relative to VPR default settings                         | . 50 |

| Table 8 Runtime Speedup of iPlace relative to VPR "-fast" settings                         | . 50 |

| Table 9 Runtime Speedup of iPlace relative to VPR "-superfast" settings                    | . 51 |

| Table 10 Average Displacement Results for Synthetic Benchmark Circuits, Baseline V Default |      |

| Table 11 Average Displacement Results for Synthetic Benchmark Circuits, iPlace             | . 54 |

| Table 12 PR 2.5 and 5 Benchmark Statistics                                                 | . 56 |

| Table 13 PR 10 and 15 Benchmark Statistics                                                 | . 56 |

| Table 14 Runtime Speedup of iPlace relative to VPR default settings                        | . 57 |

| Table 15 Runtime Speedup of iPlace relative to VPR "-fast" settings                        | . 57 |

| Table 16 Runtime Speedup of iPlace relative to VPR "-superfast" settings                   | . 58 |

| Table 17 Average Displacement Results from PR Benchmark Circuits, VPR "Default"            | .61  |

| Table 18 Average Displacement Results from PR Benchmark Circuits, iPlace                   | . 61 |

| Table 19 Multi Region 50 and 40 Benchmark Characteristics                                  | . 63 |

| Table 20 Multi Region 30 and 20 Benchmark Characteristics                                  | . 63 |

| Table 21 Multi Region 10 Benchmark Characteristics                                         | . 63 |

| Table 22 Runtime Speedup of iPlace relative to VPR default settings                        | . 65 |

| Table 23 Runtime Speedup of iPlace relative to VPR "-fast" settings                        | . 65 |

| Table 24 Runtime Speedup of iPlace relative to VPR "-superfast" settings                   | . 65 |

| Table 25 Multi Region Run-time Speedup Summary                                                                          |

|-------------------------------------------------------------------------------------------------------------------------|

| Table 26 Overall Run-time Speedup Summary                                                                               |

| Table 27 Single-Region Synthetic Benchmark Circuit Statistic                                                            |

| Table 28 Single-Region Synthetic Benchmark Circuit Statistic Cont'                                                      |

| Table 29 Single-Region Synthetic Benchmark Placement Results                                                            |

| Table 30 Single-Region Synthetic Benchmark Placement Results cont'                                                      |

| Table 31 Single-Region Synthetic Benchmark Placement Results cont'                                                      |

| Table 32 Single-Region Synthetic Benchmark Placement Results cont'                                                      |

| Table 33 Relative performance VPR "-default" versus iPlace                                                              |

| Table 34 Single-Region Synthetic Benchmark Placement Results: Relative performance VPR "-default" versus iPlace Cont'   |

| Table 35 Single-Region Synthetic Benchmark Placement Results: Relative performance VPR "-default" versus iPlace Cont'   |

| Table 36 Single-Region Synthetic Benchmark Placement Results: Relative performance VPR "-default" versus iPlace Cont'   |

| Table 37 Single-Region Synthetic Benchmark Placement Results: Relative performance VPR "-fast" versus iPlace            |

| Table 38 Single-Region Synthetic Benchmark Placement Results: Relative performance VPR "-fast" versus iPlace Cont'      |

| Table 39 Single-Region Synthetic Benchmark Placement Results: Relative performance VPR "-fast" versus iPlace Cont'      |

| Table 40 Single-Region Synthetic Benchmark Placement Results: Relative performance VPR "-fast" versus iPlace Cont'      |

| Table 41 Single-Region Synthetic Benchmark Placement Results: Relative performance VPR "-superfast" versus iPlace       |

| Table 42 Single-Region Synthetic Benchmark Placement Results: Relative performance VPR "-superfast" versus iPlace Cont' |

| Table 43 Single-Region Synthetic Benchmark Placement Results: Relative performance VPR "-superfast" versus iPlace Cont' |

| Table 44 Single-Region Synthetic Benchmark Placement Results: Relative performance VPR "-superfast" versus iPlace Cont' |

| Table 45 Single-Region Synthetic Benchmark Placement Results: Placement Stability for VPR Baseline          |

|-------------------------------------------------------------------------------------------------------------|

| Table 46 Single-Region Synthetic Benchmark Placement Results: Placement Stability for iPlace                |

| Table 47 Single-Region Physical Resynthesis Benchmark iPlace Placement Results 103                          |

| Table 48 Single-Region Physical Resynthesis Benchmark Relative Performance, VPR default versus iPlace       |

| Table 49 Single-Region Physical Resynthesis Benchmark Relative Performance, VPR "-fast" versus iPlace       |

| Table 50 Single-Region Physical Resynthesis Benchmark Relative Performance, VPR "-super-fast" versus iPlace |

| Table 51 Multi Region Physical Re-Synthesis Benchmark iPlace Placement Results 107                          |

| Table 52 Multi Region Physical Re-Synthesis Benchmark Relative Performance, VPR default versus iPlace       |

| Table 53 Multi Region Physical Re-Synthesis Benchmark Relative Performance, VPR "-fast" versus iPlace       |

| Table 54 Multi Region Physical Re-Synthesis Benchmark Relative Performance, VPR "-super-fast" versus iPlace |

|                                                                                                             |

## **List of Figures**

| Figure 1 Island Style FPGA                                            | 5  |

|-----------------------------------------------------------------------|----|

| Figure 2 BLE and CLB                                                  | 6  |

| Figure 3 FPGA Routing Architecture                                    | 8  |

| Figure 4 FPGA CAD Flow                                                | 10 |

| Figure 5 Simulated Annealing Algorithm                                | 14 |

| Figure 6 Initial Layout                                               | 26 |

| Figure 7 Super-grid Expansion Pseudocode                              | 28 |

| Figure 8 Super Grid Expansion                                         | 29 |

| Figure 9 Multi-region floorplan handling                              | 30 |

| Figure 10 Compaction Regions                                          | 32 |

| Figure 11 Compaction Pseudocode                                       | 33 |

| Figure 12 Supergrid Compaction Moves                                  | 34 |

| Figure 13 Final Legalized Solution                                    | 34 |

| Figure 14 Channel Width tradeoff versus Alpha and Number of Swaps (S) | 36 |

| Figure 15 Critical Path tradeoff versus Alpha and Number of Swaps (S) | 37 |

| Figure 16 Channel Width versus Run-time Trade off while tuning iPlace | 38 |

| Figure 17 Critical Path versus Run-time Trade off while tuning iPlace | 38 |

| Figure 18 Stratix II FPGA layout                                      | 41 |

| Figure 19 Handling Carry chains                                       | 42 |

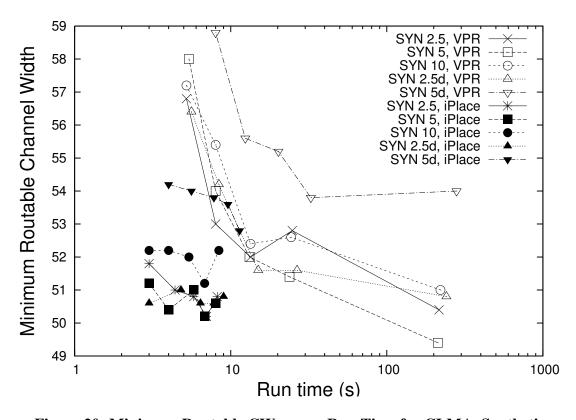

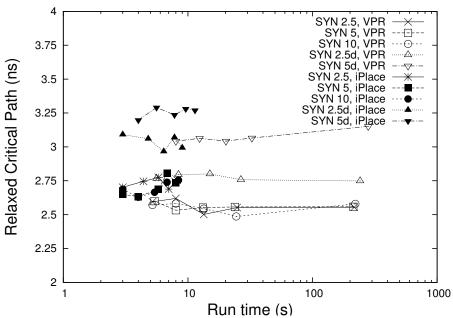

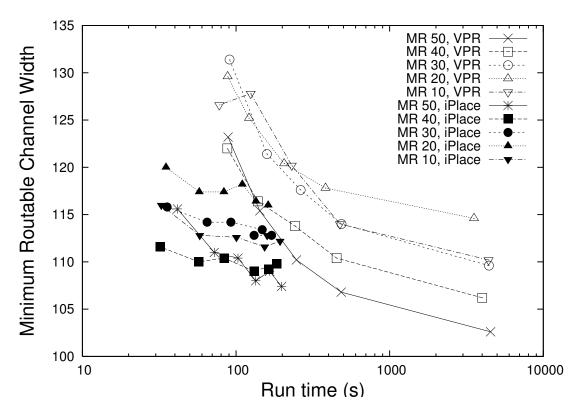

| Figure 20: Minimum Routable CW versus Run Time for CLMA, Synthetic    | 52 |

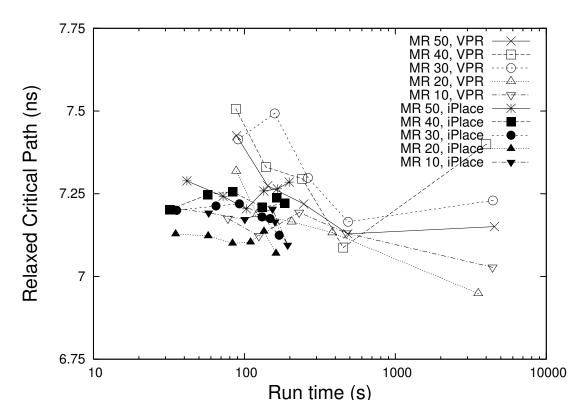

| Figure 21: Relaxed Critical Path versus Run Time for CLMA, Synthetic  | 53 |

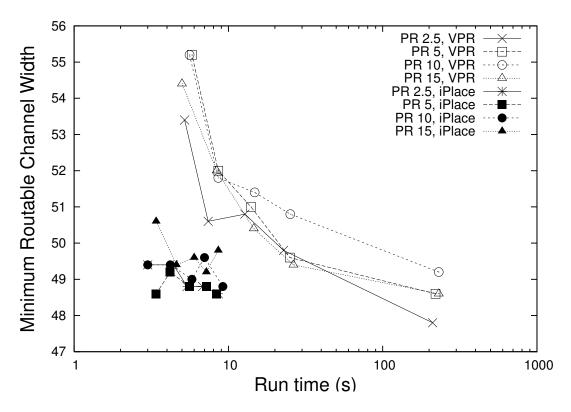

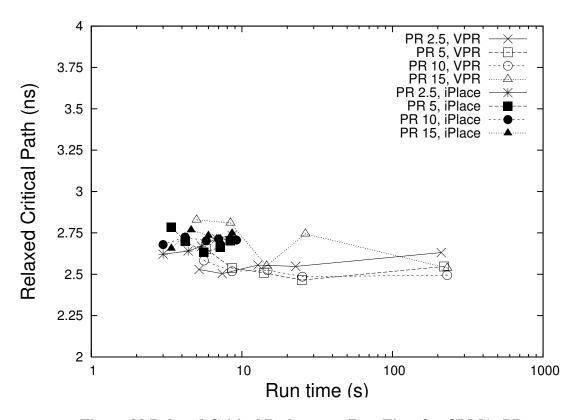

| Figure 22 Min. Routable Channel Width vs. Run Time for CLMA, PR       | 59 |

| Figure 23 Relaxed Critical Path versus Run Time for CLMA, PR          | 60 |

| Figure 24 Minimum Routable CW versus Run Time for Stdev010, MR        | 66 |

## Glossary

Application Specific Integrated Circuit (ASIC):

An integrated circuit designed for a specific purpose

Basic Logic Element (BLE):

Basic logic element of an FPGA that consists of a

K-input lookup table and a flip-flop.

Computer Aided Design

(CAD) Tools:

A set of software tools for designing systems,

semiconductor systems in particular

Clustered Logic Blocks

(CLB):

Logic Block of an FPGA, comprised of N BLEs clustered together with fast local interconnect

Field Programmable Gate

Array (FPGA):

An integrated circuit containing programmable logic elements and programmable routing. An FPGA can be

programmed to implement any digital circuit

iPlace: An incremental placement tool designed for FPGA CAD

flows

Interconnect Resource Aware Clustering (iRAC): FPGA clustering algorithm [25]

Look Up Table (LUT): A memory cell capable of implementing any K-input, 1

output logic function.

MicroElectronics

Corporation of North

Carolina (MCNC) Circuits:

A standard set of benchmark circuits used in the FPGA

academic community [66]

Minimum Routable Channel

Width (MRCW):

The minimum number of routing tracks per channel a

FPGA must have to successfully route a particular

circuit

T-V Pack: FPGA clustering algorithm [8]

Un/Do Pack: An FPGA channel width reduction tool that can target

hard channel width constraints to achieve routing

closure [1]

Versatile Place and Route

(VPR):

An academic placement and routing tool for FPGAs [32]

## Acknowledgements

First of all, I would like to thank my graduate supervisor, Dr. Guy Lemieux for having me as his student. Even though I had a full time job aside from this Masters degree, he was patient and supportive throughout the last two years. I am especially grateful for the times Dr. Lemieux was willing to stay late to accommodate my working schedule. Without his brilliant ideas and meticulous screening of my work, I could not have come this far.

I would also like to thank Marvin Tom for getting me started in the field of FPGA research. Without his guidance and help, I would not have been able to quickly learn the intricate details of conducting research. It was a pleasure to work with Marvin on Un/DoPack and the ICCAD paper.

To my best friends, Derek, Patrick and Stephen<sup>1</sup>, thank you for the great times we have had since elementary school. My life would be very boring without your company.

Finally, I would like to thank Westgrid for providing the computational resources used to perform the simulations for this thesis. The amount of computation required would not have been possible without the use of the UBC Glacier cluster.<sup>2</sup>

<sup>&</sup>lt;sup>1</sup> In alphabetical order =)

<sup>&</sup>lt;sup>2</sup> WestGrid is funded in part by the Canada Foundation for Innovation, Alberta Innovation and Science, BC Advanced Education and the participating research institutions. WestGrid equipment is provided by IBM, Hewlett Packard and SGI

## **Dedication**

-To my family, thank you for all your support, patience and love during the last few years.

### 1. Introduction

Field Programmable Gate Arrays (FPGAs) are a specialized type custom integrated circuit. FPGAs are capable of implementing any digital circuitry through the use of reprogrammable look up tables and routing fabric. Compared to ASICs, FPGAs offer a low cost alterative to designing digital circuitry. FPGAs allow designers to quickly prototype and test a circuit on hardware, without the need for expensive mask and foundry costs associated with ASIC designs. However, there are drawbacks of using FPGAs compared to ASICs. ASICs offer much higher chip density, faster clock speeds as well as lower power usage. The tradeoffs associated with ASICs and FPGAs depend on the sales volume of the final product. ASICs are more suited to large volume, high performance devices such as microprocessors. FPGAs on the other hand are more suitable for medium-to-small volume devices or devices that require fast time to market.

As the logic capacity of FPGAs increases with deep submicron technology, the run time required to compile and fit a high level design onto a target FPGA increases significantly. Recompiling the design from scratch for small changes or localized improvements is a time-consuming operation. For today's largest FPGAs, a full recompilation often requires several hours to execute the entire FPGA CAD flow.

Often only a small section of the circuit is modified, thus raising the need for incremental algorithms that can speed up the compilation process. The need for incremental algorithms extends beyond small design changes. For circuits designed using design hierarchy, multiple sub-circuits can be modified concurrently by several designers. The need for incremental CAD techniques that can quickly integrate multiple changes together are

necessary for fast turn around time. In addition, sub-circuits can be re-used multiple times in a design. Modifications to one such sub-circuit require changes to multiple regions across the FPGA. Incremental techniques must be able to handle the use cases outlined above. In addition, incremental techniques must be scalable for small-to-large modifications to ensure the most efficient use of development time. The resulting incremental compilation for such use cases should be as high quality as compilation from scratch.

### 1.1. Contributions

This thesis presents an incremental placement algorithm named "iPlace" to be used as part of an incremental CAD flow. Our approach uses existing academic tools as a foundation and extends them for incremental placement. Results from this work appeared in [1]. A paper describing the algorithm details has been submitted for review [2].

The iPlace algorithm starts with an initial high-quality placement of a "before" circuit prior to modification. For this, we use the default VPR placement algorithm. The "before" state is used as a reference solution for incremental placement. Next, iPlace finds a new placement for the modified "after" circuit state. The "after" state is the new circuit to be incrementally placed using iPlace. The iPlace algorithm produces the new placement solution through four phases: (1) use the "before" state to produce an initial placement of the unmodified CLBs, (2) insert modified CLBs by shifting into a *super-grid*, (3) compact the super-grid by shifting to re-legalize placement, and (4) refine with a low-temperature anneal. The *super-grid* is a placement grid that is extended beyond the bounds of the initial FPGA device.

Three key ideas are present in the iPlace algorithm. The first idea is the use of floor-planning constructs to constrain the initial placement of modified CLBs close to the original placement "hole" left by the removal of some CLBs from the "before" state. These floor-planning constraints are continuously modified as the algorithm executes. The second idea is a "placement super-grid". The super-grid expands the entire placement region as more CLBs are added than the "hole" permits. The third idea is the use of partial design shifting during the expansion and compaction phases of the algorithm. Shifting partial rows/columns of CLBs is much more CPU-efficient than relying upon individual moves used in annealing-based approaches, particularly because annealing must also measure the cost of each LE move before deciding. After the shifting, a low temperature simulated annealing run is performed to improve the solution quality. This annealing step is the slowest step. These steps combine to produce a fast and high quality incremental placement algorithm

To measure the performance of the incremental placement algorithm, we developed three sets of benchmarks. Each individual benchmark circuit has a "before" and "after" state. The first set of benchmarks approximate incremental design changes where subregions of a circuit are significantly modified in logic and structure but other regions are untouched. This set is created using a synthetic circuit generator to mutate a selected subregion of the circuit. These clones are re-stitched into the original circuit [3] [4]. The second benchmark set approximates a physical resynthesis flow where the circuit is logically identical, but functionally-equivalent changes are made within one local region. The second benchmark set is automatically produced from a physical resynthesis CAD flow [1]. The third benchmark set is a variation of the second, but scaled to include multiple regions of design changes. This set, also produced using [1] is used to determine the ability of iPlace in

handling multiple design changes across large regions of the chip.

## 1.2. Thesis Outline

The remainder of this thesis is organized as follows. First, Chapter 2 will present background information on FPGAs and prior work related to incremental placement. Next, Chapter 3 will describe the iPlace algorithm in detail. Chapter 4 will present the results of benchmarking iPlace with the three benchmark sets. Chapter 5 presents a qualitative comparison of iPlace against existing fast and incremental approaches. Finally, Chapter 6 summarizes the key contributes and results of iPlace.

## 2. Background

This chapter presents the background information related to FPGAs and incremental placement research. First, the hardware architecture and makeup of FPGAs will be presented. Second, the software CAD flow related to compiling designs for FPGAs will be discussed. Finally a summary of prior work related to incremental placement will be presented.

## 2.1. FPGA Architecture

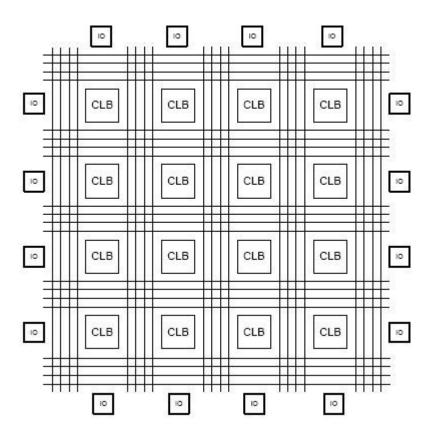

Figure 1 Island Style FPGA [5]

Field Programmable Gate Arrays (FPGAs) are Very Large Scale Integrated (VLSI) circuits that are capable of implementing *any* user designed digital circuit. FPGAs offer this

flexibility of through the use of reconfigurable Logic Elements (LE). The typical layout of an FPGA circuit used by commercial devices such as Altera's Stratix [6] and Xilinx's Virtix [7] is shown in Figure 1. The layout style of the FPGA shown in Figure 1 is called an Island Style Architecture. The Island Style FPGA consists of clusters of LEs called Configurable Logic Blocks (CLB). The CLBs are laid out in a rectangular array surrounded by configurable routing wires in both the vertical and horizontal directions. The *Array Size* of an FPGA is measured in terms of the number of CLBs spanning horizontally and vertically. The name "Island" architecture comes from the fact that CLBs "islands" are surrounded by a sea of configurable wires. Around the periphery of the chip are Input/Output (IO) pads to connect the FPGA to the rest a circuit design.

#### **Logic Element and Clustered Logic Blocks (LE and CLB)**

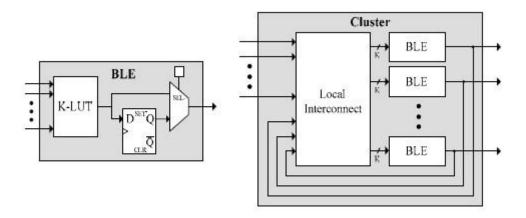

Figure 2 BLE and CLB [5]

The most basic element of a FPGA is the Basic Logic Element (BLE or LE). The logic element consists of a K-input look up table, a flip-flop and a multiplexer (Figure 2). The k-input LUT is capable of implementing any k-input, 1 output combinational logic function. A LUT is made of 2<sup>K</sup> configuration bits that can be programmed to implement the desired logic function. The flip-flop provides synchronous output for the logic function

implemented by the LUT. Finally, the multiplexer allows the selection of the combinational or synchronous output for the BLE.

From prior research [8], it was shown that it is more efficient to pack multiple LEs into a *cluster* called a Configurable Logic Block (CLB). The structure of a CLB is shown in Figure 2. Each cluster contains N LEs. The number N is typically  $4^3$ ,  $8^4$ ,  $10^5$  or  $16^6$  logic elements [6][7]. Each LE within the cluster is interconnected to each other with fast local interconnect. The number of inputs to a CLB I, is smaller than the maximum K\*N because LEs can share common inputs. The advantages of packing multiple LEs into a cluster include reducing delay, reducing the amount of interconnect required, more dense FPGA designs and improved CAD compilation runtime.

<sup>&</sup>lt;sup>3</sup> Xilinx Virtex

<sup>&</sup>lt;sup>4</sup> Xilinx Virtex II

<sup>&</sup>lt;sup>5</sup> Altera Cyclone, Altera Stratix

<sup>&</sup>lt;sup>6</sup> Altera Cyclone II

#### **Routing Architecture**

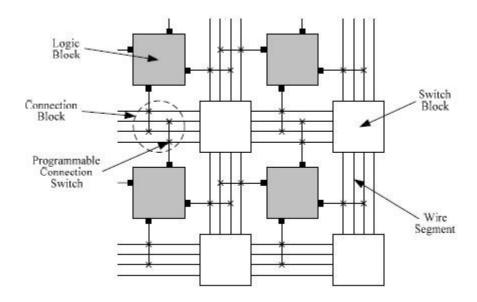

Figure 3 FPGA Routing Architecture [5]

The second component that makes up an FPGA is the routing architecture. The routing architecture is responsible for connecting the reconfigurable CLBs together to form the overall design. The routing architecture is comprised of three components: wires, switch blocks and connection blocks [9]. A simplified view of the routing architecture is shown in Figure 3. First, wires are the core of the routing structure. Wires fill the vertical and horizontal channels in between rows/columns of CLBs. In commercial FPGAs, multiple length wires spanning 4, 8, 16 and 24 or greater number of CLBs [6] are provided for the different routing requirements of each net. Shorter wires are for local interconnection, whereas longer wires are designed to connect CLBs far apart with less delay. Wires can be can designed to carry signals bi-directionally or uni-directionally, although the latter has been shown to be faster and consume less area in recent research [10]. The second component is the switch block. The switch block connects vertical and horizontal wires so that signals can switch directions or extend the length of a wire past the length of a segment. The third component is the connection block. The connection block connects CLBs to their

adjacent wires. In bidirectional interconnect, the switch and connection blocks are often fabricated using tri-state buffers or pass transistors, and controlled using sram programming bits. In unidirection interconnect, the switch and connection blocks are fabricated with multiplexers, tri-state buffers and controlled using sram. The routing architecture is the predominant contributor to the FPGA die size, speed and power requirements.

#### **Commercial devices:**

| Part                 | EP1S10 | EP1S20 | EP1S25 | EP1S30 | EP1S40 | EP1S60 | EP1S80 |

|----------------------|--------|--------|--------|--------|--------|--------|--------|

| Logic Capacity       | 10,570 | 18,460 | 25,660 | 32,470 | 41,250 | 57,120 | 79,040 |

| <b>Channel Width</b> | 160    | 160    | 160    | 160    | 160    | 160    | 160    |

Table 1 Altera Stratix Family of FPGAs [6]

Commercial devices measure the logic *capacity* of a FPGA in terms of the number of the number of LEs. The routing *capacity* is measured in terms of the number of routable wire segments passing between adjacent CLBs. This fixed routing capacity is called the *Channel Width* of a device. Commercial devices also contain multiplier and memory blocks that are not within the scope of this work. Commercial devices are usually offered as "families" of FPGAs, where the channel width remains the same within a family, but the array size is increased to offer larger logic capacities for different family members. An example of an FPGA family from Altera is presented in Table 1. The latest FPGAs offered by Altera and Xilinx have logic capacities exceeding 200,000 LEs. [6][7][11]

### 2.2. FPGA CAD Flow

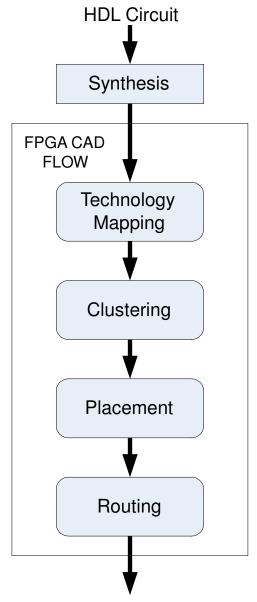

FPGA Programming bit stream

**Figure 4 FPGA CAD Flow**

To develop a circuit for use on a FPGA, designers use high level languages such as VHDL or Verilog to describe the circuit behavior. A multi-stepped CAD flow is required to compile the circuit description from the high level language description to programming the LUTs and switches of the FPGA. This CAD flow consists of five steps. The first step is

synthesis. In this step, the circuit description is compiled from the high level language to a network of Boolean equations and flip-flops. The synthesis step is common to both ASIC and FPGA development. The FPGA specific portion of the CAD flow consists of technology mapping, clustering, placement and finally routing. In this section, each step of the FPGA CAD flow will be presented.

### 2.2.1. Technology Mapping

The first step in the FPGA CAD flow is technology mapping. In this step, the Boolean network is mapped to the look-up table size of the FPGA. The goal of technology mapping is to use as few LEs as possible to minimize logic usage and circuit delay. Technology mapping algorithms minimize the delay of a circuit by minimizing the *logic depth*, which is the longest path of a circuit. Several technology mapping algorithms are presented in [12][13][14][15][17][18][19][20][21].

The most notable technology mapping algorithm for FPGA is FlowMap [12][13]. The FlowMap algorithm was revolutionary as the algorithm is able to produce a depth optimal solution in polynomial complexity time. This algorithm is based on network flow algorithms using the *max-flow-min-cut* theorem. The results reported in [12] shows that FlowMap produces better critical path and area results compared to other technology mapping algorithms at the time. Follow-ups to the FlowMap algorithm include CutMap [14][15] and DAOMap [16] . CutMap improved on FlowMap by reducing logic duplication. Logic duplication occurs during the FlowMap algorithm when a node is encapsulated (duplicated) by multiple LUTs in the technology mapping solution. CutMap is able to reduce the number of logic elements required by 20% compared to FlowMap while maintaining depth-optimality in the solution.

### 2.2.2. Clustering

The second step in the FPGA CAD flow is clustering. In this step, the technology mapped K-input LUTs are packed clusters of size N defined by the FPGA architecture. The goal of clustering is to maximize utilization of the cluster resources, minimize delay and to reduce the amount of interconnect required between clusters. Clustering algorithms can be classified into three categories. The most common algorithms are bottom-up [8][22][23][24][25]. Bottom up algorithms greedily builds each cluster by selecting a seed LE and growing by individual LEs. The second type of clustering algorithm is top-down [26][27]. Top-down algorithms start with the entire technology mapped circuit, and recursively partitions the circuit into bins until each bin reaches the cluster size. The final type of clustering algorithm is depth optimal clustering [28][29][30]. Depth optimal clustering minimizes delay in exchange for more logic use due to duplication.

Bottom up algorithms are the most common category employed for FPGAs, so the bottom up approach will be discussed in this section. Bottom up algorithms begin each cluster by selecting a seed LE based on an algorithm specific criterion. The algorithm then iteratively selects the next most attractive LE using an attraction function to add to the cluster. Once a cluster is full, a new seed is chosen for a new cluster. The process is repeated again until all LEs are clustered.

Criticality(b) =

$$1 - \frac{\text{slack(b)}}{\text{max\_slack}}$$

(1)

$$Attraction(b,c) = \alpha * crit(c) + (1-\alpha) * \frac{nets(b) \cap nets(c)}{G}$$

(2)

A widely cited academic FPGA bottom-up clustering algorithm is T-VPack [8]. T-VPack is a timing aware algorithm that aims to minimize both the delay and the number of nets to

route. The seed for each cluster is chosen as the most timing critical LE. The equation to calculate the criticality of an LE "b" is given in (1). Additional LEs are added to the cluster using the attraction function shown in (2). Equation (2) shows that the attraction of an element c to cluster b is a factor combining the criticality of the LE and the normalized number of nets common with the current cluster contents. The weighting factor  $\alpha$  balances the importance of timing versus the number of nets absorbed into the cluster. The factor  $\alpha$  was experimentally determined in [8] to be 0.75.

Another bottom-up clustering algorithm is iRAC [25]. iRAC is a greedy clustering algorithm that aims to minimize the number of nets to route for the computed clustering solution. The premise of the algorithm is to encapsulate as many nets as possible within a cluster, thus minimizing the number of nets required to route between clusters. iRAC also includes a cluster input limiting component computed based on the Rent parameter [31] of the cluster. The clustering algorithm used for this work is an iRAC replica produced for [1]. The iRAC replica excluded the input limiting component due to the limited improvement it offered. This algorithm was selected for use with this thesis because it produces the lowest routed channel widths and delay performance compared to TVPack [25].

#### 2.2.3. Placement

The third step in the FPGA CAD flow is placement. In this step, the clustered LEs are mapped to physical CLB locations on the FPGA. The goal of placement is to minimize both the routing delays of regular nets and the delay of the critical path. The placement engine must also be congestion aware to avoid over-usage of the routing resource, which

<sup>&</sup>lt;sup>7</sup> The number of nets in common is normalized to a constant G

could lead to an un-routable solution. There are three general types of placement algorithms. First, Simulated Annealing (SA) algorithms [5][32][33][34][35] are the most common and based on a hill climbing approach. Second, Analytical Placement algorithms [36][37][38][39] solve the placement problem by using systems of equations. Analytical Placement algorithms are good at finding approximate locations for CLBs, but due to the discretization effects of mapping to an FPGA array, they often result in overlaps that need to be removed through additional re-legalization steps. Finally, Min-Cut algorithms [40][41][42] produce placement solutions using partitioning techniques. Simulated Annealing algorithms are the most common in academic research and will be presented in more detail in this section.

```

Random Placement():

2 temp = Initial Temperature();

3

R_{limit} = nx;

4

5

While( ExitConditionSatisfied() == false )

6

for(int i=0; i<inner num; ++1)

7

move = Generate Move();

8

\Delta C = Calculate Cost Delta( move );

float r = rand(0,1);

9

if( \Delta C < 0 )

10

AcceptMove( move );

11

else if( r < e^{-\Delta C/T})

12

13

AcceptMove( move );

14

end for

temp = UpdateTemperature(); // t = \alpha*t

15

16

r_{limit} = UpdateRange();

Update Net Criticality();

17

end while

18

```

**Figure 5 Simulated Annealing Algorithm**

VPR is the academic FPGA CAD tool most commonly used for FPGA research. The work

presented in this thesis is developed by extending the VPR simulated annealing placement algorithm for incremental placement. VPR features an adaptive temperature cooling schedule and range limiting techniques to produce excellent placement solutions.

The VPR simulated annealing algorithm is presented in Figure 5. The first step in the placement process is to randomly place all CLBs onto the placement array. Next, the initial temperature is determined by performing a number of test swaps equal to the number of CLBs. The initial temperature for VPR is set as 20 times the standard deviation of the cost evaluated during the test swaps. The initial range limit is set as the length or width of the device<sup>8</sup>.

$$\Delta C = \lambda \frac{\Delta \text{Timing\_Cost}}{\text{Previous\_Timing\_Cost}} + (1 - \lambda) \frac{\Delta BB\_\text{Cost}}{\text{Previous\_BB\_Cost}} (3)$$

$$\text{timing\_cost} = \sum_{\forall i, j \in circuit} delay(i, j) * crit(i, j)^{CE} \quad (4)$$

$$\text{bb\_cost} = \sum_{i=1}^{\forall nets} q(i) [bb_x(i) + bb_y(i)] \quad (5)$$

The simulated annealing algorithm works by performing *inner\_num* number of swaps at each temperature setting. For each swap, a random move is proposed by swapping the placement position of two CLBs. If the swap results in a reduction in the placement cost, the swap is accepted. If swap results in an increase in cost, a probabilistic acceptance is used based on the  $e^{-\Delta C/T}$  where  $\Delta C$  is the change in cost according to (3) and T is the current temperature. Accepting bad moves is required for hill climbing to avoid local minimums in the cost function. Equation (3) is composed of 2 terms, a timing cost and a bounding box cost. The factor  $\lambda$  is a weighting factor to balance the importance of these costs. Each term

<sup>&</sup>lt;sup>8</sup> Assuming a square array. Commercial FPGAs are rectangular.

is normalized to the total cost from the previous iteration. The timing cost shown in equation (4) is a sum of the delay\*net criticality product for each net. The net criticality is defined as (1). The bounding box cost is the sum of the Manhattan distance for each net.

After *inner\_num* number swaps are performed at each temperature range, the temperature and range limit factors are updated. The temperature is degraded using an update factor  $\alpha$ . As the temperature is lowered during the annealing process, the  $e^{-AC/T}$  term approaches 0 so that fewer bad swaps are accepted for hill climbing. Both  $\alpha$  and the range limit are adaptively adjusted to keep the swap acceptance rate at ~44%. The 44% acceptance rate was shown to be the optimal hill climbing factor in [43].

$$t < \frac{0.005 * cur\_cost}{num nets}$$

(6)

The algorithm terminates when the exit criterion is met. The equation for calculating the exit criteria in VPR is presented in (6)

## **2.2.4. Routing**

The final step in the FPGA CAD flow is routing. In this step, routing resources are assigned for each net of the circuit to connect the logic elements together based on the CLB placement solution from the placement stage. The goal of routing is to minimize the delay of the circuit and to avoid congestion in the routing resources. Routing algorithms can be classified into two categories. First, two-step routers [44][45][46][47][48] break down the routing process into two steps: global routing and detail routing. Second, single step global-detail routers [49][50][51][52] perform both the global and detail routing together as a single step. In global routing, the input-output pins and the routing channels are assigned to a signal. In detail routing, each signal is assigned to specific routing track

within each channel. Two-step routers are used for ASIC designs because of routing flexibilities. Single step global-detail routers are used for FPGAs due to the limited and constrained routing resource architecture.

The academic CAD tool VPR [5][32] features a two step FPGA router using the PathFinder routing algorithm [50]. PathFinder is an iterative routing algorithm based on cost sharing and track negotiations. During the initial routing iteration, all nets are routed via the lowest cost route. This produces overuse in popular tracks where multiple signals are assigned to the same track, which is illegal for a routing solution. For each iteration, all nets are ripped up and rerouted. Iteratively, the cost of the overused wire segments is increased so that nets are forced to evaluate and use different routes wherever possible. The algorithm terminates when there is no more overuse, forming a legal solution.

$$Cost(i) = Crit(i) * delay(i) + (1 - Crit(i)) * b(i) * h(i) * p(i)$$

(7)

The VPR routing cost function is shown in (7). The cost function to route each net is based on a combination of two terms. The first term represents the Elmore delay of the wire segment. The second term is based on the base  $\cos t b(n)$ , history  $\cos t h(n)$  and the present  $\cos t p(n)$ . The history  $\cos t$  represents a history of how congested a wire segment has been. The present  $\cos t$  represents the present  $\cos t$  to use a wire segment. The present  $\cos t$  is increased as the algorithm progresses to discourage over usage of wires. The weighting of each term is dependent on the criticality of the net calculated using (1). Nets on the critical path will have a criticality factor close to 1. Based on (7), the critical path net will be routed on the path with lowest delay.

## 2.3. Incremental Placement Techniques

In a traditional FPGA "full compilation" process, the entire CAD flow must be executed if

any changes are made to a circuit. To speed up this process, our flow takes an *incremental* approach: only the *changes* to the netlist are propagated through clustering and placement, and a full route is done at the end. For both incremental clustering and incremental placement, a "reference solution" computed from the previous compilation is used to identify changes and reduce the amount of new work. This section will briefly describe both of these steps, but the focus is on incremental placement.

Incremental clustering initially starts with the previous list of CLBs, a list of unmodified CLBs, and a list of unclustered logic elements. The unmodified CLBs are the same as before (they contain the exact same logic elements). In contrast, modified CLBs arise because some logic elements were *deleted* by a user logic change. Modified CLBs are unclustered into its constituent LEs, and these are added to the pool of new LEs that were *added* by the user logic change.

Incremental clustering proceeds as follows. The unmodified CLBs are kept as-is. Due to their greedy nature, clustering algorithms such as TVPack [8] and iRAC [25] can easily treat these unmodified CLBs as an intermediate solution and continue grouping the unclustered logic elements into new CLBs. Since all flip-flop locations in the entire circuit are known, incremental clustering can still identify critical paths and remain timing-driven. Our implementation uses the iRAC replica, since it produces good timing results and requires the lowest channel width for routing. The clustering tool then proceeds to form new CLBs using the new LEs and LEs from unmodified CLBs

Incremental placement initially starts with the previous placement of CLBs, a list of unmodified CLBs, a list of removed CLBs, and a list of new CLBs. In the event of multiple

changes<sup>9</sup>, the list of new CLBs (and removed CLBs) is divided into a number of sub-lists, one for each change or each instance. Optionally, a rectangular floorplan constraint for each change can be given. If none is provided, the bounding box for each "removed CLB sub-list" is computed and applied as a floorplan constraint to the corresponding "new CLB sub-list".

Incremental placement proceeds as follows. The unmodified CLBs are re-placed in their previous location to preserve "spatial locality", i.e., physical closeness to their connected neighbours. For each "region" of change, the placement locations previously occupied by the removed CLBs are now left empty, thus leaving white space for the new CLBs. For the new CLBs, two cases must be considered. If there are fewer new CLBs, they all fit in the white space left behind and placement is "trivial". The second case to consider is when the new CLBs exceed the removed CLBs. Since there is insufficient room, unmodified CLBs must be moved to make room or new CLBs will be placed far away. This is the key problem to solve for incremental placement. To maintain placement locality, most incremental placement algorithms temporarily allow overlap, which is when multiple CLBs occupy the same physical location. Overlap results in an illegal solution which must be fixed through a lengthy re-legalization step. Instead, iPlace immediately shifts other CLBs out of the way and continues. This is called expansion. By the end, CLBs are often pushed past of the limits of the array, which is also illegal. iPlace then re-legalizes by compacting: it forcibly shifts available whitespace along the edges to where it is needed, thus making room for the illegal CLBs. Finally, this legal placement is refined through annealing.

\_

<sup>&</sup>lt;sup>9</sup> Due to component re-use, multiple instances of the same circuit are treated as multiple changes.

Incremental placement algorithms have not been widely published. Cong and Sarrafzadeh [53] give high level overviews of the problems associated with incremental CAD, including placement. They note two separate needs for incremental placement: to optimize an existing good placement for a new metric, or for handling the addition and removal of logic or nets. iPlace is designed for the latter situation.

Previously published algorithms for incremental placement in FPGAs include work by Singh and Brown [54], Suaris et al [55] and Togawa et al [56]. Both [54] and [55] are intended to be used with physical resynthesis to assist with timing closure, while [56] is a congestion-driven approach. A comparative summary follows.

The Singh and Brown placer, ICP [54], is primarily focused on improving timing through small netlist changes, such as retiming register moves. As a result, it operates on changes at the logic element (LE) level. Initially, ICP allows all LEs to be assigned to their preferred location, which may be illegal, for best timing performance. Then, it iteratively moves each LE, using a negotiation similar to PathFinder, to legalize conflicts and reduce timing and estimated wiring costs. It considers individual LE moves, and evaluates the cost of each one. Since it considers only a small number of moves, it is about 8 times faster than VPR. In contrast, iPlace is about 60 times faster than VPR because it operates at the CLB level and does not evaluate individual move costs when resolving illegal placements. Instead, iPlace presumes that shifting imposes a minimal cost penalty during legalization and uses simulated annealing at the end to improve or recover lost quality.

Suaris et al present an incremental placer in a framework called IPR [55] which has very

similar goals and operation to ICP. However, IPR uses quadratic placement to assign initial placements, which also results in overlaps. Like ICP, IPR also performs individual LE moves and evaluates the cost of each one during legalization – however, the IPR costs appear to be entirely timing-driven. No run-time results were reported for IPR; hence it cannot be directly compared to iPlace.

Togawa et al present a congestion-driven incremental placer [56] that shifts overlapping individual LEs to reduce global routing capacity. It avoids increases in channel width for up to 20% changed LEs. In contrast, we have observed that iPlace can tolerate changes to 2/3 of all CLBs without inflating channel width, critical path or wirelength.

Previous work on incremental placement for standard cells includes papers by Choy et al [57], J. Li et al [58], and Z. Li et al [59]. The two algorithms in [57] insert one cell at a time by computing the most desired location and the lowest-cost shift sequence of the nearest empty cell. The approach in [58] eliminates overlap by shifting entire floorplan rectangles; however, it assumes significant whitespace gaps between rectangles. The approach in [59] inserts one cell at a time into optimal position, and each time it legalizes by solving an integer programming problem that determines how to shift the fewest cells the least distance. Both [57] and [59] are meant for very small netlist changes and would likely be too slow for use within iPlace. If an original floorplan is available, [58] would be useful. However, iPlace does not presume any floorplanning – it constructs its own floorplan constraints using information from the changed elements.

The final type of incremental placement algorithms are commercial tools such as Altera's Quartus II and Xilinx's ISE. These tools also support incremental compilation. The tools

have an advertised speedup of 2-3 times for the entire FPGA CAD flow when comparing an incremental compilation versus a full compilation. The details of the algorithms employed by the commercial tools are proprietary and not known in detail.

The approaches taken by previous incremental algorithms all involve solving the problem of overlaps. The algorithms start with an initial best but illegal placement, then iteratively resolves the illegal locations using different schemes until a valid placement is produced. In comparison, iPlace approaches the overlap problem in a novel manner. Instead of allowing overlaps in the first place, a CPU efficient shifting scheme is used to shift entire rows or columns of CLBs to create more white space for insertion. The shifting is followed by a fast and tuned simulated annealing (VPR) run for optimization.

## 2.4. Fast Placement Techniques

In addition to incremental placement techniques, fast placement techniques can also be considered for incremental placement. Fast placement techniques sacrifice quality in exchange for faster run time. Several fast placement techniques by Hauck et al. [60], Sankar et al. [61] and Tessier [62] evaluate different algorithms and tradeoffs for faster placement.

Hauck et al. [60] presents several fast placement techniques including partitioning, force-directed and simulated annealing algorithms. The techniques were evaluated by their run time versus critical path quality tradeoff. The best quality results were achieved with simulated annealing (VPR). To reduce run-time, the *inner\_num* parameter was varied to reduce the number of swaps. By reducing the run-time, it was found that a 20 times speed up resulted in a 2x increase in critical path. It was also found that a 2.5 times speedup had a 1.34x increase in the critical path. Force-directed placement techniques had similar run-time trade offs as simulated annealing. In comparison to iPlace, iPlace is capable of 60x speedup with no quality degradation. The approach of reducing the *inner\_num* parameter to reduce run-time is common between [60] and iPlace.

Sankar et al. [61] presents a fast placement technique based on multi-level clustering and fast simulated annealing refinement. The algorithm performs recursive bottom up clustering to form clusters of CLBs. After each stage of clustering, each cluster is internally placed constructively and refined using a retuned simulated annealing algorithm (VPR). Although only wire-length results were presented, the tool produced better quality results compared to VPR (non-timing driving) in "-fast" mode with similar run time.

Tessier [62] presents the Frontier fast placement system used in conjunction with pre-fabricated macro blocks. The Frontier approach is similar to Sankar et al. where clustering is used to group CLBs [macro blocks for Frontier] prior to simulated annealing refinement. The Frontier system was designed to place groups of pre-placed CLBs as macro blocks. The Frontier system has a reported 17x speedup compared to commercial Xilinx software.

In summary, fast placement techniques employ a variety of different methods to speed up the run-time. One common attribute to all three algorithms is the use of a retuned, fast simulated annealing (VPR) refinement scheme to improve quality. This approach is also adopted by iPlace to refine the incremental placement solution after the expansion and compaction phases. The run time of these fast algorithms are comparable to iPlace. The main difference is the quality of the placements produced. iPlace is able to produce placement solutions as *high* quality as complete placement from scratch. In comparison, the fast placers trade the decreased runtime with significantly reduced quality.

# 3. iPlace Algorithm

This chapter provides an in depth explanation of the iPlace algorithm. The iPlace algorithm is a 4 step approach to incremental placement. The core idea of the placer is based on spatial locality. If an element was previously placed at a particular location, then it is very likely that it should be placed at the exact same location (or nearby) after the circuit has been modified. A second paradigm employed by iPlace is *simplicity*. iPlace avoids the use of heavy computation for the first three phases, and only uses limited annealing to cleanup the final solution. The limited use of annealing or other computational intensive algorithms is key to iPlace's performance. The four phases of iPlace are as follows:

- 1. Initial Placement and Floorplanning

- 2. Super-grid Expansion Placement

- 3. Compaction (Re-legalization)

- 4. Refinement by Low Temperature Annealing

The iPlace algorithm is implemented in the VPR framework. Three inputs are required for the incremental placement process. The first input is an initial placement from the "before" circuit state. The second input is a *floorplan* or rectangular region identifying approximately where to place the changed elements. The third input is the modified or "after" circuit state. iPlace identifies which CLBs are *modified* and which are *unmodified* by comparing the first and third input data.

# 3.1. Initial placement

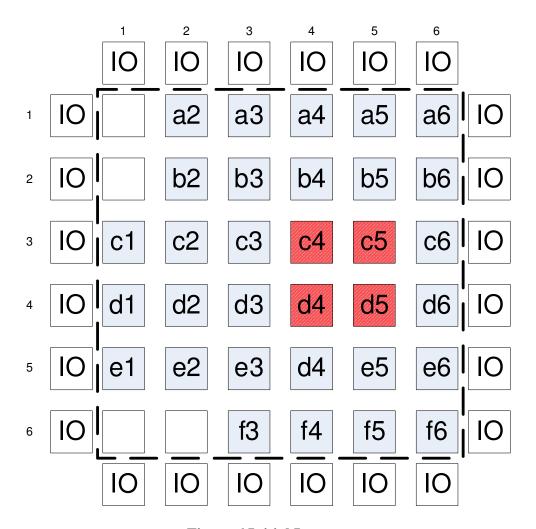

**Figure 6 Initial Layout**

The first phase of iPlace is to provide an initial placement for all *unmodified* CLBs by examining the placement solution of the "before" circuit state. This step is pictorially shown in Figure 6. The labelled cells represent unmodified CLBs; these are initially placed in their previous placement locations to maintain spatial locality. The hashed cells represent CLBs that have been modified. These are removed from the initial placement, leaving holes to be filled in later by the *modified* CLBs.

### 3.2. Floor-planning

The holes left behind by the removed elements are also the basis for floor planning. The argument is that any modified CLBs should be placed where the holes were created to preserve spatial locality. iPlace is actually capable of handling *multiple modification regions*. For each hole left behind by a group of modified CLBs, a floorplan rectangle can be generated to guide the replacement CLBs into that specific region. For the example in Figure 6, a floorplan rectangle is generated at location (4, 3), with a size of 2x2.

In this thesis, we are not overly concerned with the precise method of identifying a floorplan region as part of the incremental placement algorithm. Floorplans can also be constructed with the following methods. First, CAD tools already allow designers to floorplan the usage of a device. These constraints can be translated into incremental floorplan regions based on the modifications made on the circuit. The use of design hierarchies and SOC methods can also be used to create floorplan regions. The placement region of each component in the hierarchy can be used to dictate the region specified for incremental changes. Finally, incremental placement required for iterative re-synthesis CAD flows are also supported by iPlace. Algorithms that target constraints such as the most congested regions can directly translate the re-synthesized areas into floorplan constraints.

### 3.3. Expansion

Figure 7 Super-grid Expansion Pseudocode

The second phase of iPlace is the insertion of the *modified* CLBs into the placement grid. Each modified CLB is associated with a floorplan region. The floorplan is used give a rough initial location or area where the modified CLB should be placed. The number of modified CLBs could exceed the number of free spaces available in the floorplan area. In the expansion phase, a CPU efficient shifting scheme is used to overcome the limitation of insufficient placement locations. This phase is called "expansion" because the shifting allows CLBs to be shifted *outside* of the normal placement area. This increases or *expands* the placement grid to create more room. We call the result a "super-grid", which includes the original placement area and all of the outside areas. Precise pseudocode for this step is shown in Figure 7. The algorithm will be explained as follows using an example.

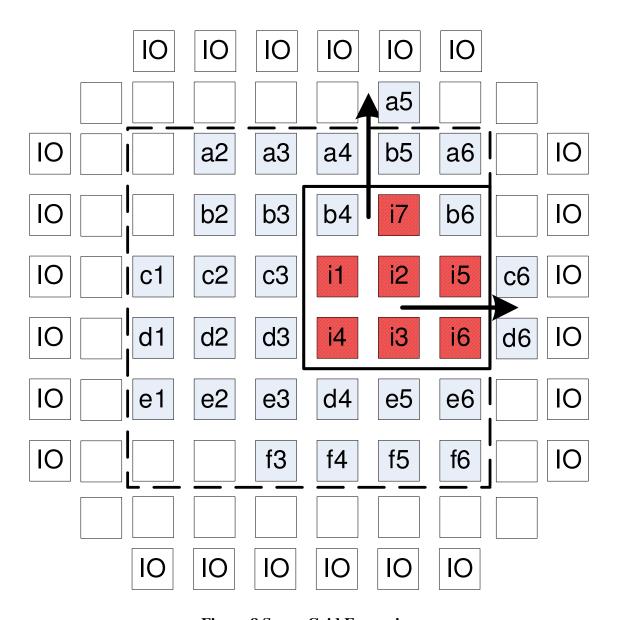

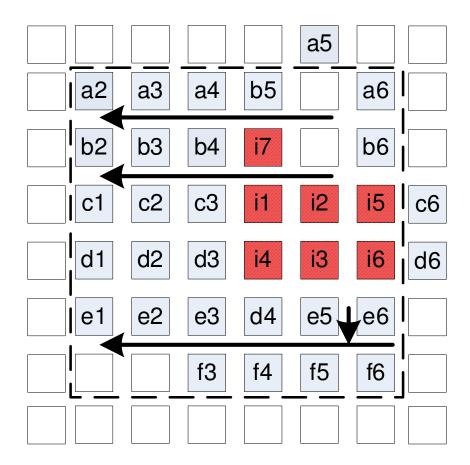

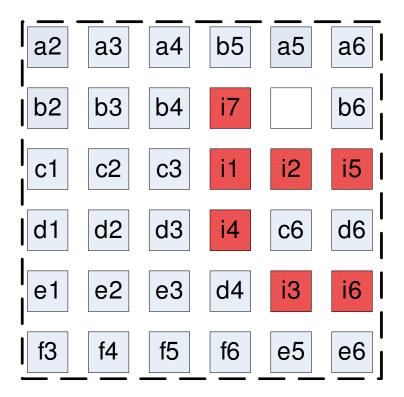

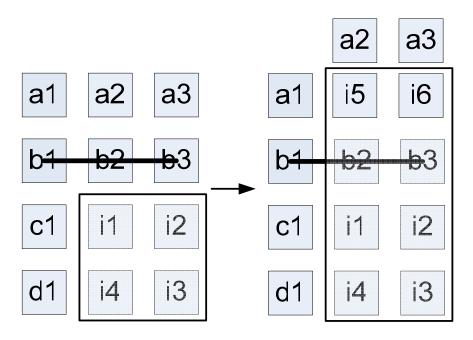

**Figure 8 Super Grid Expansion**

Referring to the example started in Figure 6, the cells c4, c5, d4 and d5 were marked for removal. These cells will now be replaced with cells i1 to i7. Note that only four free locations are available, but seven new blocks needs to be placed. Blocks i1 to i4 are randomly placed in the free locations without issue. However, there is insufficient room for blocks i5 to i7. To solve the problem of inserting more elements than the amount of free space available in the floorplan region, we use a virtual placement grid called a super-grid

that is larger than the physical FPGA size. If the region runs out of space, CLBs to the right of the region are shifted right by 1 CLB location and the floorplan rectangle is increased in width by 1. This is shown in Figure 8, where c6 and d6 are shifted right to make room for i5 and i6. Once the right side is fully shifted by 1 position, the algorithm switches to shifting CLB columns on the top side by 1 position upwards; this is shown in Figure 8 where a5 is shifted up to make room for i7. Whenever needed, the supergrid size array is increased, adding additional rows and columns. Note that the IO locations just shift outwards but are not reordered or increased in number. The super-grid allows the algorithm to shift CLBs to locations *outside* of the normal placement area. This avoids the need for additional calculations to re-shuffle free spaces within a limited placement area, but preserves the *relative* placement of most CLBs with the intent of benefiting from the original spatial locality.

Figure 9 Multi-region floorplan handling

Since iPlace is a multi-region incremental placement algorithm, it must be able to handle multiple floor-planned areas supporting overlaps and expansion of each area individually. To maintain placement locality, the shifting paradigm does not move any affected floor

plans when shifting is required. Instead, all affected floor plan regions increase in size along the shifting rows or columns. This idea is graphically illustrated in Figure 9. Two floor planned areas named i and j are shown. If placement region i was to expand upwards by 1 row, floorplan j becomes affected. Instead of moving the entire region j upwards, only the required columns are shifted up (j1 and j3). Both regions i and j increase in size by 1 vertically. Note that regions i and j now overlap. The free element introduced is common to both regions i and j. If region j required more space, it can take advantage of the shifting done for region i and use the newly created free locations.

**Observation 1:** The shifting paradigm is CPU efficient. It does not need CPU intensive cost function calculations or any sort of iterative location evaluation. The algorithm evenly distributes the expansion across the four sides.

**Observation 2:** The amount of shifting required to expand a region is quite modest. For example, to expand a 5x5 CLB region by 20%, only one shift on one side is required to make it 5x6. The limited shifting maintains placement locality and does not significantly disturb the overall relative ordering of CLBs in the original placement.

### 3.4. Compaction

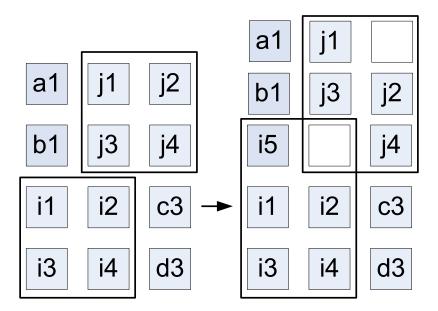

**Figure 10 Compaction Regions**

The third phase of iPlace is to re-legalize the placement. After the super-grid expansion phase, there could be CLBs located outside of the legal placement area defined by the FPGA array size. One method to re-legalize all CLBs is to use an annealing algorithm. However, this is a slow process and does not guarantee that all CLBs will eventually converge to legal areas. Instead, we propose a *simple* and *fast* solution called "compaction" to overcome this problem. Note that the super-grid can be partitioned into 9 sections like a "#" sign, with the legal placement area at the centre. This is graphically shown in Figure 10 where "R" represents the Regular placement area, S represents Side and C represents Corner. This leaves four corners and four sides to handle. The algorithm works by shifting *all* of the free space (empty CLBs) spread throughout the legal placement region to one end. The algorithm performs horizontal followed by vertical compaction to move free space to the required side (or vice versa for different cases). For the four corners, compaction is

done to move the space to the corner. For the four side cases, the free spaces are first percolated to the required side. A centroid position is calculated to estimate where the bulk of the illegal cells are located. The free space is shifted to the centroid location to preserve locality. The centroid location is calculated as the median position for all illegal CLBs located on the side under consideration. Following compaction, the illegal cells are randomly re-inserted into the legal free space. The pseudocode for the compaction algorithm is shown in Figure 11

```

for each illegal region r

{

if r is corner

{

shift all free space to corner

randomly move illegal cells in free space

}

if r is side

{

shift all free space to side

find centroid of illegal placements in r

shift free space to centroid

randomly move illegal cells in free space

}

}

}

```

Figure 11 Compaction Pseudocode

**Figure 12 Supergrid Compaction Moves**

**Figure 13 Final Legalized Solution**

Continuing with the example from Figure 6 and Figure 8, the compaction process is graphically shown in Figure 12. The block a5 is re-legalized by compacting the free space from the top left corner. Note that the free space has percolated from the top left corner to the locations below a5. The cells c6 and d6 are re-legalized by first compacting the free space from the bottom left hand corner. This percolates the free space to the bottom right hand corner. Next, cells e5 and e6 are compacted downwards to the bottom right hand corner. The final legalized solution is shown in Figure 13.

### 3.5. Refinement

After the compaction step, we found that the average bounding box and critical path delays were not ideal. In most cases, the bounding box cost reported by VPR was 20% larger than a full placement from scratch. The estimated critical paths were also 10% higher. To refine the solution, we added a low temperature annealing step to iPlace. The refinement phase must not disturb the spatial locality property that iPlace is based upon, but must also be able to perform limited hill climbing to optimize the modified CLBs. To accomplish this task, we re-tuned various parameters within the simulated annealing algorithm of VPR. To limit hill climbing, the *initial temperature* was lowered so that fewer "bad" swaps would be accepted. To maintain spatial locality, the initial window range was lowered to focus the swaps within a more localized area. To reduce and control the runtime, the number of swaps per temperature range factor *inner\_num* and the temperature degradation factor alpha parameters were also tuned.

The initial temperature was selected as the first 44% acceptance rate cross over point during the baseline initial placement. The 44% acceptance rate threshold was chosen based on previous work in [43].

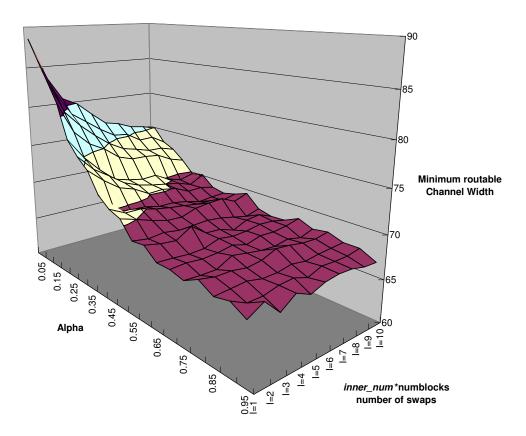

Figure 14 Channel Width tradeoff versus Alpha and Number of Swaps (S)

Figure 14 shows the channel width quality trade off versus temperature degradation (alpha) and the number of swaps *inner\_num* (*I*)\*numblocks per temperature range. At very low alpha factors, substantially more swaps are required to refine the solution. Very low values represent a rapid cooling schedule. Even with a larger number of swaps, low alpha ranges are unable to produce high quality solutions. There is a 10% channel width degradation when comparing an alpha of 0.95 versus an alpha of 0.05 for a swap multiplier S of 10. A more substantial 50% degradation is observed when an alpha value of 0.05 is used with value S of 1. For the refinement stage of iPlace, a conservative alpha factor of 0.45-0.50 and an *inner\_num* multiplier N of 1 to 3 would suffice to produce a high quality channel placement with respect to channel width.

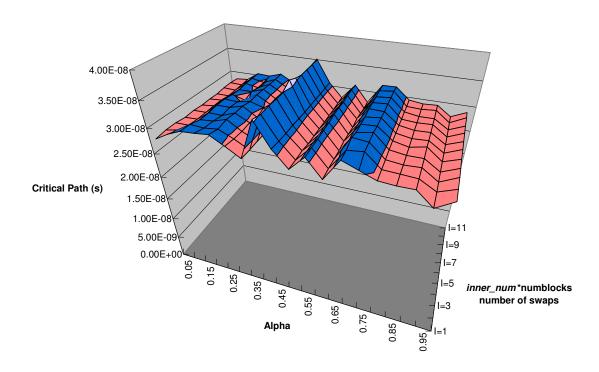

Figure 15 Critical Path tradeoff versus Alpha and Number of Swaps (S)

Figure 15 shows the critical path trade off versus alpha and number of swaps N. The figure shows that the critical path is somewhat noisy for varying values of alpha. The reasoning behind this could be explained by the rapid cooling effect for lower values of alpha. If insufficient hill-climbing is performed, then the solution could be easily trapped by local minimums. This is especially important because iPlace bases the incremental solution on prior placements. If the previous solution was sensitive to begin with, the incremental placement could be greatly affected. From Figure 14, Figure 15 and other tuning trials (not shown), it was determined that an alpha value of 0.7 or above produced the best results.

The final tuned parameters after simulation were found to be the following:

- Initial temperature of 44% acceptance rate from previous placement

- Initial window range of 12.5% of the FPGA width

- Temperature degrading factor *alpha* of 0.7

- Number of swaps per temperature range, *inner\_num* of 1 to 3

Based on the tuning, the refinement phase optimizes the placement and produces a high quality result that is comparable to a full placement. The run-time is also very short, and is controllable via the *inner\_num* parameter.

# 3.6. Additional Tuning Considerations

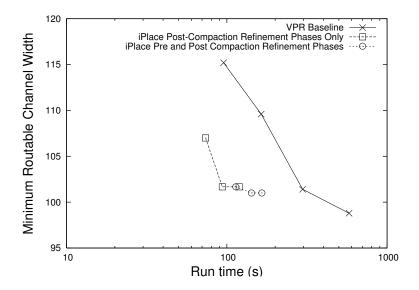

Figure 16 Channel Width versus Run-time Trade off while tuning iPlace

Figure 17 Critical Path versus Run-time Trade off while tuning iPlace

During the design and tuning of the iPlace algorithm, the amount of refinement using

simulated annealing was considered a crucial parameter. The refinement stage makes up the bulk of the runtime but is required to produce the highest quality solutions. During the design and tuning of iPlace, it was also considered to have an additional refinement stage in between the expansion and compaction stages. The goal of this additional refinement stage was to reduce the amount of illegal CLBs located outside of the legal placement area. The hope was that with fewer illegal CLBs, the amount of compaction required would be minimized. The pre-compaction refinement stage used the same tuning parameters as the post-compaction refinement stage. The initial temperature was lowered to the 44% threshold, *alpha* was reduced to 0.7 and the *inner\_num* parameter varied from 1 to 2 to control the run-time. Tuning was done with 60,000 LUT synthetic circuits produced for [1].

Figure 16 and Figure 17 shows the channel width and critical path versus run-time trade off of having the additional refinement stage before compaction. Figure 16 shows the addition of the pre-compaction refinement stage does help to lower the minimum routable channel width. However, increasing the *inner\_num* parameter for the post-compaction refinement stage can make up for the loss of the pre-compaction refinement phase. The crossover point at 100 seconds shows that the post-compaction stage alone can still achieve the same results as having both the pre and post compaction refinement phases but with faster runtime. Figure 17 shows the critical path versus run-time for the same comparison. There are no notable quality differences for the critical path results with the addition of the pre-compaction refinement. Based on these results, it was decided to only have a post-compaction refinement stage.

### 3.7. Algorithm Conclusions

This chapter has presented an incremental placement algorithm iPlace to be used as part of an incremental CAD flow. The iPlace algorithm was designed based on the principles spatial locality and efficient shifting algorithms. The four steps to the iPlace algorithm include initial placement, controlled expansion, compaction and retuned simulated annealing refinement. The initial placement phase places all unmodified CLBs at their previous placement locations. The expansion phase uses floor-planning and shifting to place all modified CLBs into an expanded placement grid. The compaction phase re-legalizes the placement also by shifting. Finally, the refinement phase produces a high quality incremental placement by cleaning up the intermediate solution with a fast and retuned simulated annealing algorithm.

# 3.8. Algorithm Limitations

iPlace currently does not take into account that commercial FPGAs have carry chains and hard macro blocks such, memories and multipliers. The current version of VPR is unable to model such constraints. This section will present how we envision handling these cases in the future.

# Macroblocks, Memories and Multipliers:

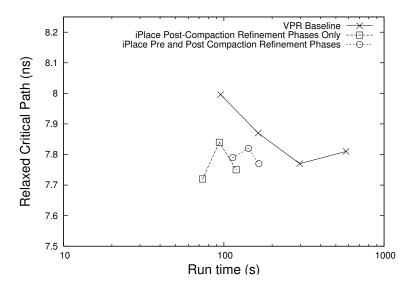

Figure 18 Stratix II FPGA layout [63]

The layout of macro blocks are usually arranged as entire columns in the FPGA array. This is graphically shown in Figure 18 with the layout of an Altera Stratix II FPGA. One way to handle these cases is to divide the placement grid into multiple vertical stripes of CLBs. Each stripe is bounded on the left and/or right by hard macro blocks. By partitioning the FPGA into multiple stripes, each partition can be considered separately for the shifting and super-grid. Other shifting constraints can also be imposed on the shifting algorithm to handle limitations such as the input positions to the macro blocks.

# **Carry Chains:**

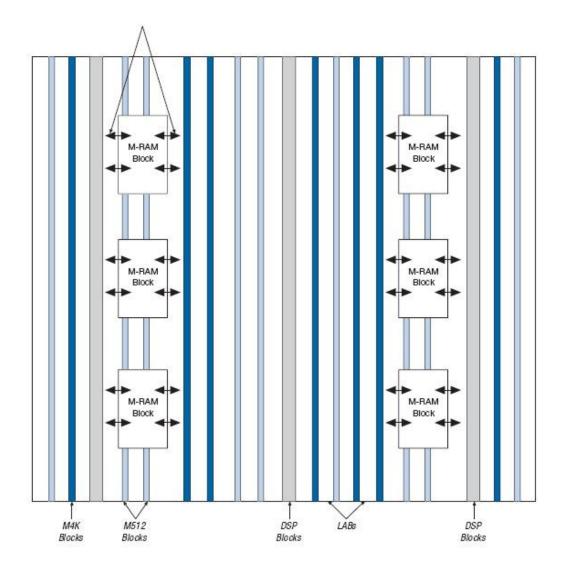

Figure 19 Handling Carry chains

The second constraint currently not handled by iPlace is carry chains. Since carry chains must remain tightly connected, the shifting process cannot destroy these placements. A potential solution to this problem is to lock down the position of carry chains. Taking into account the modest shifting requirements noted in the shifting algorithm, it is possible to fix the carry chain placement location and shift the elements over the carry chain. This is graphically shown in Figure 19. A pre-existing carry chain spans CLBs b1, b2 and b3. An incremental placement region is shown as the bounded box. If the region needs to be expanded to accommodate more elements, the floorplan can be expanded *beyond* the carry chain. The resulting placement does not disturb the carry chain but still allows for the expansion paradigm. The implementation and evaluation of these suggested changes are left for future work.

### 4. Results

This chapter details the experimental setup and the results obtained when incremental placement is performed using the iPlace algorithm. First, an overview of the experimental goals will be presented. Second, the experimental process and setup will be outlined. Third, the benchmark setup and results for the Single-Region Synthetic benchmark (SYN) set will be presented. Fourth, the benchmark setup and results for the Single-Region Physical Re-Synthesis benchmark (PR) set will be presented. Last, Multi-Region Physical Re-Synthesis benchmark (MR) set will be presented. This chapter concludes with a summary and discussion of the results for incremental placement using iPlace.

## 4.1. Experimental Goals

#### **Incremental Placement Runtime**

The main goal to measure for iPlace is the placement Run-Time (RT) of the algorithm. iPlace is an incremental placement algorithm targeted at reducing the placement run time for iterative development. The main point of comparison will be the runtime required for the baseline VPR toolset to perform a placement solution using default options. In addition, the runtime of the VPR tool set using reduced-quality settings "-fast" (*inner\_num=1*) and "-superfast" (*inner\_num=0.125*) modes will be contrasted. The "-fast" mode is a standard option available in VPR. The "-superfast" mode was developed in this thesis to compare results against very fast placement.

### **Minimal Routable Channel Width**

The second quality to measure for iPlace will be the Minimal Routable Channel Width (MRCW). The MRCW quality signifies the routability quality for a placement. This is an important factor to consider because commercial FPGA devices have fixed channel widths. If a bad incremental placement solution is created, this could lead to higher channel width requirements that cannot be satisfied by the device. To determine this quality, iPlace will be compared against VPR in default, "-fast" and "-superfast" modes.

#### **Relaxed Critical Path**

The third quality to measure for iPlace is the relaxed Critical Path (CP). The relaxed critical path is determined by routing the placement solution at 20% above the minimum routable channel width. This ensures that no portions of the FPGA are severely routing congested to obscure the true critical path. The critical path of a circuit is the longest delay path that a signal has to traverse from an input to an output or between synchronous flip-flops. The critical path determines the clock speed of a circuit, and thus its performance. To determine this quality, iPlace will be compared against VPR in default, "-fast" and "-superfast" modes.

#### **Placement Stability**

The last quality to measure is placement stability. Placement stability is a measure of how much the placement has been modified from the "before" circuit state to the "after" circuit state. There is no standard way to measure this, so we have decided to measure the total Euclidean distance traveled in the array ("before" position to "after") by all of the *unmodified* CLBs. The goal of placement stability is to show that incremental placement using iPlace results in a placement closely resembling the initial placement solution.