Our first lecture is on January 5. Labs start January 15.

I've placed copies on the shared Sharefile folder "ELEX 7660 Software". You can download the software from there if you are having problems getting the software from the Intel website: http://dl.altera.com

Are available outside my office (SW1-3061).

Avoid using bitmaps (screen captures) to include code in your reports. Use one of the methods described in the document "Including Code in Reports" under Content / Resources / Other.

Your reports do not need to include anything that is not explicitly requested in the lab instructions (e.g. an Introduction or Conclusions section). Typically, labelled listings and screen captures along with answers to any questions are all that's required for Pre-Lab and Lab reports.

If you're having problems, I strongly recommend posting to the course discussion forum rather than e-mailing me directly. You'll get a faster response since I get an e-mail notification when you post and I give replies to posted questions priority over individual e-mails. You'll also be helping your fellow students who are having the same problem. If you prefer, you can post anonymously (to other students).

I neglected to hand out Lab 2 at the lecture on Tuesday but it's available on D2L (here).

There are copies on the wall by the door to my office.

Your one-page project abstract with the names of the team members and an outline of the project objectives is due Wednesday, January 31. You can enroll yourselves by using the Groups link on the course navigation bar. You'll need to do this before you can submit your project documents.

Based on a few initial submissions, I may have downplayed my expectations for what you should submit for your abstract.

Your mark for the project outline will be proportional to the amount of effort and thought that you put into it.

While your abstract only needs to be one page long, that page should demonstrate that you've done some research and put some thought into what you want to do.

A half-page document with a vague and unoriginal idea, no references or diagrams (or one that doesn't include an FPGA!) will result in a poor mark.

You will spend about a person-week of effort on the project. Don't waste that time. Pick a topic that you will find interesting and will help advance your career goals.

Since only about a third of the students were able to complete Lab 4 during the scheduled lab, I will allow you to demonstrate Lab 4 either at the Tuesday lab next week or at the start of the Lab 5 session without penalty. I will be in the lab next Tuesday (February 13) during the regular lab session (2:30 to 4:30).

If you are having problems debugging your hardware I have put documentation on how to use the SignalTap logic analyzer under the Content/Labs.

Some other hints for Lab 4:

We will have two 50-minute midterm exams during the regular lecture times on Tuesday, February 20 and Friday, February 23.

The exams will cover the material from the first four lectures.

I suggest reviewing the learning objectives for each lecture (given in italics at the start of each handout) and then doing the relevant questions from the mid-term and final exams last year (available on my course archive site).

As was the case last year, the first exam will concentrate on System Verilog and the second on converting Verilog to/from schematics.

Due to today's closure of BCIT, we will have to postpone the midterm exam until a future date.

If you would like your ID card to enable access to the SW1-3060 lab for project work, please indicate this by filling out the following survey form: Access to SW1-3060

You must do this by this Friday (March 2) since we will only make one request.

Note that you must press "Submit" (not just "Save") for your answer to be recorded.

The postponed second midterm will be held on Tuesday, March 6 from 12:30 to 1:20 PM.

This exam will concentrate on converting System Verilog to/from schematics.

Since most of the class will shortly have access to SW1-3060, I need to remind you that drinks are not allowed in this lab. There is a small room accessible through a door at the rear of the lab that has a counter and sink. There you may drink, store or dispose of your beverages.

As explained in the Project Guidelines, before connecting any of the following:

As of March 26 no groups have had their interface designs reviewed so no group should be connecting their FGPA board to any of the above.

Unfortunately, I'll be unable to hold office hours on Tuesday April 10 due to a committee meeting.

You can e-mail me questions or use the course discussion forum.

Since there is an exam on Friday, the last lecture has to be cancelled.

I was going to cover the learning objectives for the course and go over last year's exam. The learning objectives are given in the second paragraph in italics at the start of each set of lecture notes and are the items that can be examined.

Last year's final exam and solutions is available on my course notes archive. This might be useful for review.

The course information document says you will need to submit:

"A final report fully documenting what was achieved. It should include block diagrams, schematics, code listings, photos, etc.)"

In response to a question about report length on the discussion forum I added:

Take a look at the reports submitted for the project courses at other Universities/Institutes.

- It would be nice if you explained the motivation behind the project.

- Your report should briefly summarize what your project does and how it works so the reader doesn't have to look at your design documents to figure it out.

- The bulk of the report should be enough technical detail (block diagrams, state machine diagrams, schematics, Verilog code, program listings, photos, plans, 3D images, etc.) so another student can (easily) understand and reproduce your project.

Somewhere on the order of 10 to 30 pages should be sufficient to describe your project. [But feel free to make your report longer or shorter if necessary.]

Remember that your report will be published. Review the guidelines in the course information handout regarding including personal information in the report (e.g. don't include your BCIT ID number).

Some other suggestions:

I will not be in my office on Friday, April 13 so the deadline to return components has been extended to the following Friday, April 20.

During the exam week I will have office hours in my office (SW01 3061) on:

You can return your components during office hours or immediately after the exam (which is on Friday from 13:30 to 16:30).

Note that you will not receive a mark for the course until the lab kit and project components are returned.

You will not receive a mark for the project report unless you've submitted a signed release form (LIB 73) to the appropriate dropbox.

A surprising number of students submitted incomplete Distribution Licenses. In many cases the form only had signatures and no other information (perhaps expecting me to fill it out?), in other cases only one student signed.

If you got a mark of zero for your Distribution License then something is wrong and you need to fix the issue and re-submit it or you will not get a mark for the report.

Many of the issues with the licenses turned out to be due to my Python script removing the contents of editable form fields (!).

I've verified the licenses manually and updated the marks. The only remaining problems are due to a few groups missing one or all signatures.

All items have been marked and the unofficial final marks are available. Please let me know if you have any questions (before Monday, May 14 if at all possible).

I can scan and e-mail your final exam to you if you'd like to see how it was marked.

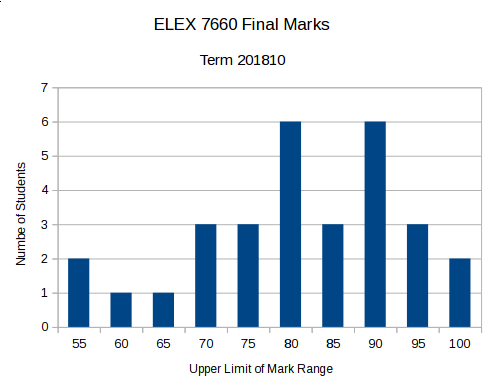

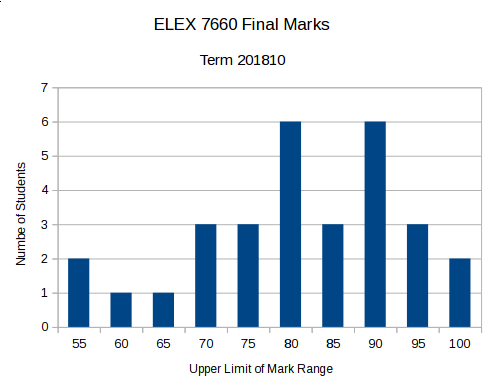

The distribution of the final marks is shown below: