## **State Machines**

This lecture describes how to design state machines and implement them using System Verilog. After this lecture you should be able to: design a state machine based on an informal description of its operation, document it using state transition diagrams and tables, and write a synthesizable Verilog description of it.

#### Introduction

A state machine<sup>1</sup> is a device whose outputs are a function of previous inputs. A state machine therefore has memory. The contents of this memory are called the "state."

Devices are often described as state machines. We will learn to describe state machines and to implement them using digital logic circuits.

## **Mealy vs Moore State Machines**

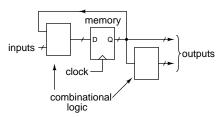

We can distinguish two types of state machines. The outputs of a *Moore* state machine are only a function of the current state:

whereas in the *Mealy* state machine the output is a function of the current state and the current inputs:

Moore state machines are simpler and have the advantage that "registered" outputs change only on the clock edges. This avoids glitches resulting from different propagation delays through the combinational logic at the output. This is desirable for signals that go off-chip. However, since the outputs of a Moore state

machine change only on clock edges they cannot respond as quickly to changes in the input.

**Exercise 1:** Which signals in the above diagrams indicate the current state?

**Exercise 2:** Which outputs are registered? Which outputs could change whenever the input changes?

# **Design of State Machines**

The following steps can be used to design a Moore state machine. This initial design may need to be refined by adding or removing states or changing the transitions conditions until the solution meets the requirements.

#### **Step 1 - Inputs and Outputs**

The first step is to accurately identify the inputs and outputs. This is important because the rest of the design effort will be wasted if necessary inputs or outputs are not included in the design.

The outputs will generally be specified in the requirements. You should ensure the selected inputs are sufficient to provide the desired behaviour.

#### Step 2 - States

The second step is to identify a sufficient number of states.

Since the output of a Moore state machine depends only on the previous inputs we could – in theory – use a shift register to store previous inputs and use combinational logic to compute the current output from the contents of the shift register. However, in most cases it's possible to use a much more concise representation of the states.

One approach is to begin by listing all the required *combinations* of the outputs. For a Moore state machine that has only registered outputs each of these will correspond to a state.

Exercise 3: Why?

<sup>&</sup>lt;sup>1</sup>An implementable state machine has a finite amount of memory and is sometimes referred to as a "finite state machine" (FSM).

#### **Step 3 - State Transitions**

The final step is to define the behaviour of the state machine by defining:

- (i) the possible state transitions, and

- (ii) the input condition(s) required for each of these transitions.

These will depend on the specifications of the state machine.

In the process of defining the transition conditions you may find that it's not possible to unambiguously determine the next output based solely on the current output and the input. This implies that there are state variables that are do not appear in the output.

In this case you must add "hidden" states (two or more states with the same output) that allow the required state transitions to be made unambiguously.

## **State Machine Descriptions**

State machine are typically documented as a state-transition table or a state-transition diagram.

A state transitions table has columns for the initial state, the input condition(s), and the next state. The output corresponding to each different state (and inputs for Mealy state machine) can also be listed in the same or a different table.

A state machine with a small number of states can be described using a state transition (or "bubble") diagram. Each circle represents a different state and arrows represent the state transitions. Each transition is labelled with the input required for that transition and each state is labelled with a state name and, for a Moore state machine, the output for that state.

State machine descriptions often omit input conditions that don't result in a change of state and use X to indicate "don't care" values.

#### **Implementation**

## **State Encodings**

In many cases we can use the outputs themselves as state variables. This has the advantage that no additional flip-flops are necessary to obtain registered outputs. We can also use k flip-flops to represent  $2^k$  states (e.g. 3 flip-flops can encode up to 8 states).

FPGA designs often use "one-hot" encodings where one flip-flop is used for each state and only one flip-flop at a time may set to 1. This encoding requires more flip-flops but can simplify the combinational logic.

**Exercise 4:** If we used 8-bits of state information, how many states could be represented? What if we used 8 bits of state but used a "one-hot" encoding?

#### **State Transition and Output Logic**

The state transitions are implemented as combinational logic that computes the next state based on the current state and the input. In Verilog this is usually done using nested case and/or if/else statements in an always\_comb procedural block.

If some outputs are not represented by state variables then it's necessary to add combinational logic to compute these outputs based on the state and, in the case of a Mealy state machine, the inputs.

A practical circuit also needs a clock signal and a reset input. The FSM will change state on every rising edge of the clock and revert to a starting state when the reset input is asserted. Often the reset is synchronous – it is simply another input and the circuit transitions unconditionally to the required state on the next rising edge of the clock.

### **Interacting State Machines**

In practice, most systems will be composed of multiple state machines interacting with each other. For example, a multi-digit counter may be designed as a combination of individual single-digit counters each of which is designed as a state machine with a terminal-count output and a count-enable input.

**Exercise 5:** The link below describes a game. List the top-level game states. Decompose each of these into multiple states. Repeat.

Simon Game

#### **Examples**

#### **Counter**

In this example the state is the counter output. The state transition table, the System Verilog model and simulation waveforms for a 2-bit counter with reset Sequence Detector and enable inputs are shown below.

|       |     |       |        | next  |     |

|-------|-----|-------|--------|-------|-----|

| count |     |       |        | count |     |

| [1]   | [0] | reset | enable | [1]   | [0] |

| 0     | 0   | 0     | 1      | 0     | 1   |

| 0     | 1   | 0     | 1      | 1     | 0   |

| 1     | 0   | 0     | 1      | 1     | 1   |

| 1     | 1   | 0     | 1      | 0     | 0   |

| a     | ь   | 0     | 0      | a     | b   |

| X     | X   | 1     | X      | 0     | 0   |

```

// 2-bit counter with enable and

// synchronous reset

module ex22 (output logic [1:0] count,

input logic enable, reset, clk );

logic [1:0] count_next ;

// next-state logic

always_comb begin

if ( reset )

count_next = 2'b00 ;

else if ( ~enable )

count_next = count ;

case(count)

2'b00: count_next = 2'b01;

2'b01: count_next = 2'b10;

2'b10: count_next = 2'b11 ;

default: count_next = 2'b00 ;

endcase

end

// register

always_ff@(posedge clk)

count <= count_next ;</pre>

endmodule

```

Exercise 6: What happens if both reset and enable are asserted?

**Exercise 7:** Draw the state transition diagram.

**Exercise 8:** Rewrite the state transition table and the module using n and n+1.

This type of state machine is used to detect a sequence of values such as the correct combination entered into a digital lock. In this case the single-bit "unlocked" output is not enough state to determine if the correct sequence has been input.

This implementation uses a shift register to store past inputs and combinational logic to detect the required pattern (1,2,3,4 in this example) in the input.

The output is registered and will be high for one clock period when the correct sequence is recognized. A practical digital lock would change state only when a key is pressed (or released) rather than on every clock edge.

```

// digit-sequence detector

module ex24 ( output logic unlock,

input logic [3:0] digit,

input logic clk );

logic [3:0] digits[4], digits_next[4];

logic unlock_next ;

// next-state logic

always_comb begin

for ( int i=0 ; i<3 ; i++ )

digits_next[i] = digits[i+1] ;

digits_next[3] = digit ;

unlock next = digits next ==

'{ 4'd1, 4'd2, 4'd3, 4'd4 };

end

// register

always_ff@(posedge clk) begin

digits <= digits_next ;</pre>

unlock <= unlock_next ;

end

```

endmodule

## **Traffic Lights**

endpackage

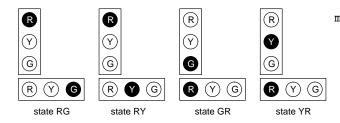

This is an example that combines two state machines: one to sequence the traffic lights at an intersection and one to implement delays. The states are encoded as the on/off values of the (Red, Green, Yellow) lights in each direction:

A package is used to define an enumerated type to label the four states (rg, ry, gr, and gy) according to the signal colors in the two directions:

```

package ex28pkg ;

typedef enum logic [5:0]

// RYG RYG

{ rg=6'b100_001, ry=6'b100_010,

gr=6'b001_100, yr=6'b010_100 }

lightstate ;

```

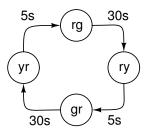

Delays are implemented by decrementing a counter on each clock edge. When the counter reaches zero the state changes and the counter is loaded with the duration of the next state.

The state transition diagram showing the duration of each state is:

The simulation outputs (with the lights shown in octal) are shown below:

The module definition is given below. The state and counter values are given initial values. On some technologies, these are the values when a device is powered up.

```

// traffic light controller

import ex28pkg::*;

module ex26 ( output lightstate lights,

input logic clk );

lightstate state=rg, state_next ;

logic [4:0] count=0, count_next;

// combinational logic

always_comb begin

// next traffic light state

state_next = state ;

if (! count)

case (state)

rg: state_next = ry ;

ry: state_next = gr ;

gr: state_next = yr ;

yr: state_next = rg ;

endcase

// duration of next state (-1)

if (! count)

if ( state == rg || state == gr )

count next = 4;

else

count_next = 29 ;

else

count_next = count-1 ;

end

// registers

always_ff@(posedge clk) begin

count <= count_next ;</pre>

state <= state_next ;</pre>

end

// output

assign lights = state ;

```

endmodule

**Exercise 9:** Write the state transition table for each state machine.