## TMS320VC5410 FIXED-POINT DIGITAL SIGNAL PROCESSOR

SPRS075A - OCTOBER 1998 - REVISED FEBRUARY 1999

- Advanced Multibus Architecture With Three Separate 16-Bit Data Memory Buses and One Program Memory Bus

- 40-Bit Arithmetic Logic Unit (ALU) Including a 40-Bit Barrel Shifter and Two Independent 40-Bit Accumulators

- 17- x 17-Bit Parallel Multiplier Coupled to a 40-Bit Dedicated Adder for Non-Pipelined Single-Cycle Multiply/Accumulate (MAC) Operation

- Compare, Select, and Store Unit (CSSU) for the Add/Compare Selection of the Viterbi Operator

- Exponent Encoder to Compute an Exponent Value of a 40-Bit Accumulator Value in a Single Cycle

- Two Address Generators With Eight Auxiliary Registers and Two Auxiliary Register Arithmetic Units (ARAUs)

- Data Bus With a Bus Holder Feature

- Extended Addressing Mode for 8M × 16-Bit Maximum Addressable External Program Space

- 64K x 16-Bit On-Chip RAM Composed of:

- Four Blocks of 2K × 16-Bit On-Chip Dual-Access Program/Data RAM

- Seven Blocks of 8K × 16-Bit On-Chip Single-Access Program/Data RAM

- 16K × 16-Bit On-Chip ROM Configured to Program Memory

- Enhanced External Parallel Interface (XIO2)

- Single-Instruction-Repeat and Block-Repeat Operations for Program Code

- Block-Memory-Move Instructions for Better Program and Data Management

- Instructions With a 32-Bit Long Word Operand

- Instructions With Two- or Three-Operand Reads

- Arithmetic Instructions With Parallel Store and Parallel Load

- Conditional Store Instructions

- Fast Return From Interrupt

- On-Chip Peripherals

- Software-Programmable Wait-State Generator and Programmable Bank-Switching

- On-Chip Programmable Phase-Locked Loop (PLL) Clock Generator With Internal Oscillator or External Clock Source

- One 16-Bit Timer

- Six-Channel Direct Memory Access (DMA) Controller

- Three Multichannel Buffered Serial Ports (McBSPs)

- 8-Bit Enhanced Parallel Host-Port Interface (HPI8)

- Power Consumption Control With IDLE1, IDLE2, and IDLE3 Instructions With Power-Down Modes

- CLKOUT Off Control to Disable CLKOUT

- On-Chip Scan-Based Emulation Logic, IEEE Std 1149.1† (JTAG) Boundary Scan Logic

- 144-Pin Thin Quad Flatpack (TQFP) (PGE Suffix)

- 176-Pin Ball Grid Array (BGA) (GGW Suffix)

- 10-ns Single-Cycle Fixed-Point Instruction Execution Time (100 MIPS)

- 3.3-V I/O Supply Voltage

- 2.5-V Core Supply Voltage

#### description

The TMS320VC5410 fixed-point, digital signal processor (DSP) (hereafter referred to as the '5410 unless otherwise specified) is based on an advanced modified Harvard architecture that has one program memory bus and three data memory buses. This processor provides an arithmetic logic unit (ALU) with a high degree of parallelism, application-specific hardware logic, on-chip memory, and additional on-chip peripherals. The basis of the operational flexibility and speed of this DSP is a highly specialized instruction set.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

† IEEE Standard 1149.1-1990 Standard-Test-Access Port and Boundary Scan Architecture.

# terminal functions

The terminal functions table lists each signal, function, and operating mode(s) grouped by function.

## **Terminal Functions**

| TERMINAL                                                                                      |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|-----------------------------------------------------------------------------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| TERMINAL<br>NAME                                                                              | 1/0†  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| DATA SIGNALS                                                                                  |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| A22 (MSB) A21 A20 A19 A18 A17 A16 A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 (LSB) | O/Z   | Parallel address bus A22 [most significant bit (MSB)] through A0 [least significant bit (LSB)]. The sixteen LSB lines, A0 to A15, are multiplexed to address external memory (program, data) or I/O. The seven MSB lines, A16 to A22, address external program space memory. A22–A0 is placed in the high-impedance state in the hold mode. A22–A0 also goes into the high-impedance state when OFF is low.  The address bus has a bus holder feature that eliminates passive components and the power dissipation associated with them. The bus holder keeps the address bus at the previous logic level when the bus goes into a high-impedance state. |  |  |  |  |

| D15 (MSB) D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 (LSB)                             | I/O/Z | Parallel data bus D15 (MSB) through D0 (LSB). D15–D0 is multiplexed to transfer data between the core CPU and external data/program memory or I/O devices. D15–D0 is placed in high-impedance state when not outputting data or when RS or HOLD is asserted. D15–D0 also goes into the high-impedance state when OFF is low.  The data bus has a bus holder feature that eliminates passive components and the power dissipation associated with them. The bus holder keeps the data bus at the previous logic level when the bus goes into a high-impedance state. The bus holders on the data bus can be enabled/disabled under software control.      |  |  |  |  |

† I = Input, O = Output, Z = High-impedance, S = Supply

# **Terminal Functions (Continued)**

| TERMINAL<br>NAME                               | vot | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| INITIALIZATION, INTERRUPT AND RESET OPERATIONS |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| ĪĀCK                                           | O/Z | Interrupt acknowledge signal. IACK indicates receipt of an interrupt and that the program counter is fetching the interrupt vector location designated by A15–A0. IACK also goes into the high-impedance state when OFF is low.                                                                                                                                                                                                                       |  |  |  |  |

| INTO<br>INT1<br>INT2<br>INT3                   | I   | External user interrupt inputs. INT0–INT3 is prioritized and is maskable by the interrupt mask register (IMR) and interrupt mode bit. INT0 –INT3 can be polled and reset by way of the interrupt flag register (IFR).                                                                                                                                                                                                                                 |  |  |  |  |

| NMI                                            | I   | Nonmaskable interrupt. NMI is an external interrupt that cannot be masked by way of the INTM or the IMR. When NMI is activated, the processor traps to the appropriate vector location.                                                                                                                                                                                                                                                               |  |  |  |  |

| RS                                             | I   | Reset. $\overline{RS}$ causes the digitial signal processor (DSP) to terminate execution and forces the program counter to 0FF80h. When $\overline{RS}$ is brought to a high level, execution begins at location 0FF80h of program memory. $\overline{RS}$ affects various registers and status bits.                                                                                                                                                 |  |  |  |  |

| MP/MC                                          | I   | Microprocessor/microcomputer mode select pin. If active low at reset (microcomputer mode), MP/MC causes the internal program ROM to be mapped into the upper 16K words of program memory space. In the microprocessor mode, off-chip memory and its corresponding addresses (instead of internal program ROM) are accessed by the DSP.                                                                                                                |  |  |  |  |

|                                                |     | MULTIPROCESSING SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| BIO                                            | 1   | Branch control. A branch can be conditionally executed when $\overline{\text{BIO}}$ is active. If low, the processor executes the conditional instruction. The $\overline{\text{BIO}}$ condition is sampled during the decode phase of the pipeline for the XC instruction, and all other instructions sample $\overline{\text{BIO}}$ during the read phase of the pipeline.                                                                          |  |  |  |  |

| XF                                             | O/Z | External flag output (latched software-programmable signal). XF is set high by the SSBX XF instruction, set low by RSBX XF instruction or by loading ST1. XF is used for signaling other processors in multiprocessor configurations or used as a general-purpose output pin. XF goes into the high-impedance state when OFF is low, and is set high at reset.                                                                                        |  |  |  |  |

|                                                |     | MEMORY CONTROL SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| DS<br>PS<br>IS                                 | O/Z | Data, program, and I/O space select signals. $\overline{DS}$ , $\overline{PS}$ , and $\overline{IS}$ are always high unless driven low for communicating to a particular external space. Active period corresponds to valid address information. $\overline{DS}$ , $\overline{PS}$ , and $\overline{IS}$ are placed into the high-impedance state in the hold mode; these signals also go into the high-impedance state when $\overline{OFF}$ is low. |  |  |  |  |

| MSTRB                                          | O/Z | Memory strobe signal. MSTRB is always high unless low-level asserted to indicate an external bus access to data or program memory. MSTRB is placed in the high-impedance state in the hold mode; it also goes into the high-impedance state when OFF is low.                                                                                                                                                                                          |  |  |  |  |

| READY                                          | I   | Data ready. READY indicates that an external device is prepared for a bus transaction to be completed. If the device is not ready (READY is low), the processor waits one cycle and checks READY again. Note that the processor performs ready detection if at least two software wait states are programmed. The READY signal is not sampled until the completion of the software wait states.                                                       |  |  |  |  |

| R/W                                            | O/Z | Read/write signal. $R/\overline{W}$ indicates transfer direction during communication to an external device. $R/\overline{W}$ is normally in the read mode (high), unless it is asserted low when the DSP performs a write operation. $R/\overline{W}$ is placed in the high-impedance state in the hold mode; and it also goes into the high-impedance state when OFF is low.                                                                        |  |  |  |  |

| IOSTRB                                         | O/Z | I/O strobe signal. IOSTRB is always high unless low-level asserted to indicate an external bus access to an I/O device. IOSTRB is placed in the high-impedance state in the hold mode; it also goes into the high-impedance state when OFF is low.                                                                                                                                                                                                    |  |  |  |  |

| HOLD                                           | I   | Hold input. HOLD is asserted to request control of the address, data, and control lines. When acknowledged by the 'VC5410, these lines go into the high-impedance state.                                                                                                                                                                                                                                                                              |  |  |  |  |

| HOLDA                                          | O/Z | Hold acknowledge. HOLDA indicates to the external circuitry that the processor is in a hold state and that the address, data, and control lines are in the high-impedance state, allowing them to be available to the external circuitry. HOLDA also goes into the high-impedance state when OFF is low.                                                                                                                                              |  |  |  |  |

| MSC                                            | O/Z | Microstate complete. MSC goes low when the last wait state of two or more internal software wait states programmed is executed. If connected to the READY line, MSC forces one external wait state after the last internal wait state has been completed. MSC also goes into the high-impedance state when OFF is low.                                                                                                                                |  |  |  |  |

† I = Input, O = Output, Z = High-impedance, S = Supply

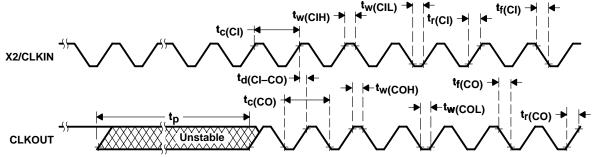

#### external multiply-by-N clock option

An external frequency source can be used by applying an input clock to X2/CLKIN with X1 left unconnected. Table 10 shows the configuration options for the CLKMD pins that generate the external divide-by-2 clock option. Following reset, the software PLL can be programmed for the desired multiplication factor. Refer to the TMS320C54x DSP CPU and Peripherals Reference Set, Volume 1 (literature number SPRU131) for detailed information on programming the PLL. The external input clock frequency is multiplied by the multiplication factor N to generate the internal CPU machine cycle.

The external frequency injected must conform to specifications listed in the timing requirements table.

#### switching characteristics over recommended operating conditions [H = (see Figure 16 and the recommended operating conditions table)

|                     | PARAMETER                                        |     | 'VC5410-100            |     |      |

|---------------------|--------------------------------------------------|-----|------------------------|-----|------|

|                     |                                                  |     | TYP                    | MAX | UNIT |

| t <sub>C</sub> (CO) | Cycle time, CLKOUT                               | 10  | t <sub>c(CI)/N</sub> † |     | ns   |

| td(CI-CO)           | Delay time, X2/CLKIN high/low to CLKOUT high/low | 3   | 6                      | 10  | ns   |

| t <sub>f</sub> (CO) | Fall time, CLKOUT                                |     | 2                      |     | ns   |

| t <sub>r(CO)</sub>  | Rise time, CLKOUT                                |     | 2                      |     | ns   |

| tw(COL)             | Pulse duration, CLKOUT low                       | H-2 | H-1                    | Н   | ns   |

| t <sub>w(COH)</sub> | Pulse duration, CLKOUT high                      | H-2 | H–1                    | Н   | ns   |

| tp                  | Transitory phase, PLL lock-up time               |     |                        | 35  | μs   |

<sup>&</sup>lt;sup>†</sup> N is the multiplication factor.

#### timing requirements<sup>†</sup> (see Figure 16)

|                     |                               |                                     | 'VC541 | 0-100 | UNIT |

|---------------------|-------------------------------|-------------------------------------|--------|-------|------|

|                     |                               |                                     | MIN    | MAX   | UNIT |

|                     |                               | Integer PLL multiplier N (N = 1–15) | 10N    | 400N  |      |

| t <sub>C(CI)</sub>  | Cycle time, X2/CLKIN          | PLL multiplier N = x.5              | 10N    | 200N  | ns   |

|                     |                               | PLL multiplier N = x.25, x.75       | 10N    | 100N  |      |

| t <sub>f(CI)</sub>  | Fall time, X2/CLKIN           | •                                   |        | 2     | ns   |

| t <sub>r(CI)</sub>  | Rise time, X2/CLKIN           |                                     |        | 2     | ns   |

| t <sub>w(CIL)</sub> | Pulse duration, X2/CLKIN low  |                                     | 2      |       | ns   |

| tw(CIH)             | Pulse duration, X2/CLKIN high |                                     | 2      | ·     | ns   |

<sup>&</sup>lt;sup>†</sup>N is the multiplication factor.

NOTE A: The CLKOUT timing in this diagram assumes the CLKOUT divide factor (DIVFCT field in the BSCR) is configured as 00 (CLKOUT not divided). DIVFCT is configured as CLKOUT divided-by-4 mode following reset.

Figure 16. External Multiply-by-One Clock Timing

## memory and parallel I/O interface timing

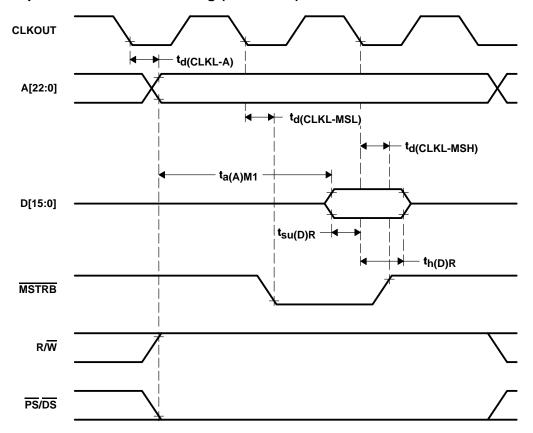

#### memory read

External memory reads can be performed in consecutive or nonconsecutive mode under control of the CONSEC bit in the BSCR.

# switching characteristics over recommended operating conditions ( $\overline{MSTRB} = 0$ ) † (see Figure 17 and Figure 18)

|                           | PARAMETER                               | 'VC5410-100 |     |      |

|---------------------------|-----------------------------------------|-------------|-----|------|

|                           |                                         | MIN         | MAX | UNIT |

| td(CLKL-A)                | Delay time, CLKOUT low to address valid | <b>–</b> 1  | 4   | ns   |

| <sup>t</sup> d(CLKL-MSL)  | Delay time, CLKOUT low to MSTRB low     | <b>–</b> 1  | 4   | ns   |

| t <sub>d</sub> (CLKL-MSH) | Delay time, CLKOUT low to MSTRB high    | <b>–</b> 1  | 4   | ns   |

<sup>†</sup> Address, R/W, PS, DS, and IS timings are all included in timings referenced as address.

# timing requirements ( $\overline{\text{MSTRB}} = 0$ ) [H = 0.5 t<sub>c(CO)</sub>]<sup>†</sup> (see Figure 17 and Figure 18)

|                     |                                                                             | 'VC5410-100 |      | UNIT |

|---------------------|-----------------------------------------------------------------------------|-------------|------|------|

|                     |                                                                             | MIN         | MAX  | UNIT |

| ta(A)M1             | Access time, read data access from address valid, first read access         |             | 4H–8 | ns   |

| ta(A)M2             | Access time, read data access from address valid, consecutive read accesses |             | 2H-8 | ns   |

| t <sub>su(D)R</sub> | Setup time, read data valid before CLKOUT low                               | 5           |      | ns   |

| th(D)R              | Hold time, read data valid after CLKOUT low                                 | 0           |      | ns   |

<sup>†</sup> Address,R/W, PS, DS, and IS timings are all included in timings referenced as address.

## memory and parallel I/O interface timing (continued)

Figure 17. Nonconsecutive Mode Memory Reads

## memory and parallel I/O interface timing (continued)

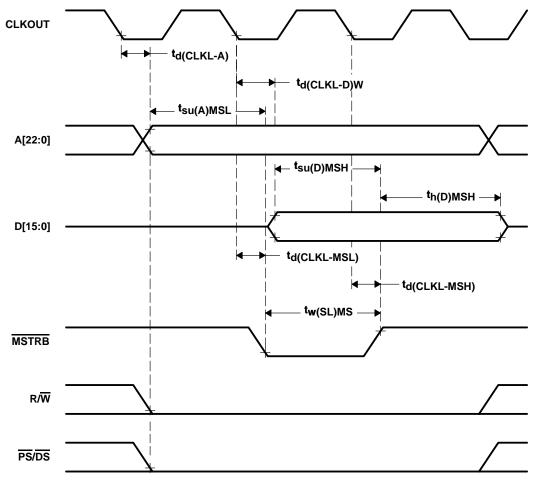

#### memory write

# switching characteristics over recommended operating conditions ( $\overline{MSTRB} = 0$ ) [H = 0.5 $t_{c(CO)}$ ]<sup>†</sup> (see Figure 19)

|                       | PARAMETER                                  |            | 'VC5410-100 |      |  |

|-----------------------|--------------------------------------------|------------|-------------|------|--|

|                       |                                            |            | MAX         | UNIT |  |

| td(CLKL-A)            | Delay time, CLKOUT low to address valid    | - 1        | 4           | ns   |  |

| t <sub>su(A)MSL</sub> | Setup time, address valid before MSTRB low | 2H – 5     |             | ns   |  |

| td(CLKL-D)W           | Delay time, CLKOUT low to data valid       | <b>– 1</b> | 4           | ns   |  |

| t <sub>su(D)MSH</sub> | Setup time, data valid before MSTRB high   | 2H – 5     | 2H + 5      | ns   |  |

| th(D)MSH              | Hold time, data valid after MSTRB high     | 2H – 5     | 2H + 5      | ns   |  |

| td(CLKL-MSL)          | Delay time, CLKOUT low to MSTRB low        | - 1        | 4           | ns   |  |

| tw(SL)MS              | Pulse duration, MSTRB low                  | 2H – 5     |             | ns   |  |

| td(CLKL-MSH)          | Delay time, CLKOUT low to MSTRB high       | - 1        | 4           | ns   |  |

† Address, R/W, PS, DS, and IS timings are all included in timings referenced as address.

Figure 19. Memory Write ( $\overline{MSTRB} = 0$ )