# **Solutions to Midterm Exam**

**Midterm 1**

### **Question 2**

# Question 1

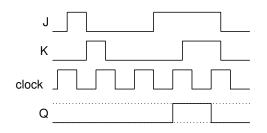

There were two timing diagrams, one for a J-K flip-flop:

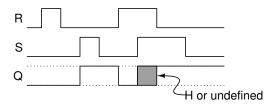

and one for an SR flip-flop:

and two truth tables, one for a T flip-flop:

| Т | CLR | clk | Q                | $\overline{Q}$   |

|---|-----|-----|------------------|------------------|

| x | 0   | x   | 0                | 1                |

| 0 | 1   | 1   | $Q_0$            | $\overline{Q_0}$ |

| 1 | 1   | 1   | $\overline{Q_0}$ | $Q_0$            |

| 0 | 1   | 1   | $Q_0$            | $\overline{Q_0}$ |

and one for a J-K flip-flop:

| J | K | CLR | clk | Q                | $\overline{Q}$ |

|---|---|-----|-----|------------------|----------------|

| x | х | 0   | 1   | 0                | 1              |

| 0 | 1 | 1   | 1   | 0                | 1              |

| 1 | 0 | 1   | 1   | 1                | 0              |

| 1 | 1 | 1   | 1   | $\overline{Q_0}$ | $Q_0$          |

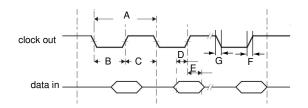

There were two timing diagrams with different labels. Only one is shown here:

On this device the clock signal is an output from the microcontroller. It is also an input to the flipflops in the peripheral device and in the microcontroller. These flip-flops store the data transmitted over the interface<sup>1</sup>.

The **clock out** signal is specified as an output so timing specifications between two points on the clock (A, B, C, G and F above) will be guaranteed specifications.

The **data** in signal is an input so timing specifications for this signal (D, E) relative to a clock edge will be requirements.

| letter   | name       | var.            | R/G |

|----------|------------|-----------------|-----|

| Α        | period     | Т               | G   |

| C<br>B+C | duty cycle | t <sub>DC</sub> | G   |

| D        | setup time | t <sub>SU</sub> | R   |

| E        | hold time  | t <sub>H</sub>  | R   |

| F        | rise time  | t <sub>R</sub>  | G   |

| G        | fall time  | t <sub>F</sub>  | G   |

#### **Question 3**

There were two versions of the question with different values. In each case the minimum clock period is  $T_{\rm min} = t_{\rm CO} + t_{\rm PD} + t_{\rm SU}$  and the maximum clock period is  $f_{\rm max} = 1/T_{\rm min}$ .

<sup>&</sup>lt;sup>1</sup>Since we had not covered this situation before, specification D will also be marked correct if specified as a propagation delay. Specification E cannot be a propagation delay because the change in the output happens before the change in the input.

- for  $t_{CO} = 3$  ns,  $t_{SU} = 5$  ns and  $t_{PD} = 8$  ns,  $T_{min} = 3+8+5 = 16$  ns and  $f_{max} = \frac{1}{16}$  GHz = 62.5 MHz

- for  $t_{CO} = 5$  ns,  $t_{SU} = 2$  ns and  $t_{PD} = 3$  ns,  $T_{min} = 5+3+2 = 10$  ns and  $f_{max} = \frac{1}{10}$  GHz = 100 MHz

# **Question 2**

There were two versions of this question, differing only in the order.

a <= b nand c ;

The figure shows a circuit that adds 1 to **Q** if **Q** is less than 3, otherwise the value is unchanged. Thus if the value of **Q** is less than 3 it increases by 1 each clock edge until it reaches the value 3. There were two versions of the question, with initial values of 1 and 0.

If the initial value is 1 then the next values in the sequence will be 2, 3, 3 and 3. If the initial value is 0, the subsequent values will be 1, 2, 3, 3.

# Midterm 2

### **Question 1**

There were two versions of this question, one turning on the warning after two faults, the other three. The three-fault version simply has one more state and is shown below.

- (a) The hint says to use the number of faults since the most recent reset as the state. We'll name them S0, S1, S2 and (optionally) S3.

- (b) The state transition diagram simply moves from one state to the next higher count when fault is asserted and to S0 when reset is asserted:

(c) In this case the output is only high in state

S3 so the expression, in VHDL format, for the

output sould be: warn <= '1' when state =

S3 else '0' ;.</pre>

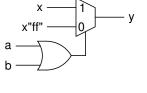

y <= x when a = '1' or b = '1' else x"ff" ;

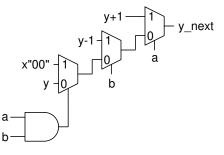

y\_next <= y+1 when a = '1' else y-1 when b = '1' else x"00" when a = '1' and b = '1' else y ;

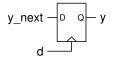

y <= y\_next when rising\_edge(d) ;</pre>

### **Question 3**

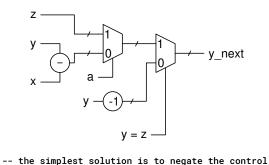

There were two version of this question differing only in the order of the block diagrams. The VHDL for each diagram is shown below: -- another solution that was accepted because it -- was not explicitly disallowed is to use an -- intermediate variable:

tmp <= z when a = '1' else y-x ; y\_next <= tmp when y = z else y-1 ;</pre>

c <= a nor b ; -- or c <= not ( a or b ) ;

$$x \xrightarrow{--1} y \xrightarrow{--1} y_{next}$$

y\_next <= x when c = '1' else y ;</pre>

c <= a when not ( b = '1' ) else 'Z' ;

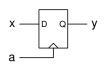

y <= x when rising\_edge(a) ;</pre>

```

-- input of the highest-priority multiplexer

-- the condition could be:

--

y /= z

-- best

-- OK

--

not (y = z)

--

( y = z ) = false -- should work

y_next <=

y - 1 when y /= z else

z when a = '1' else

y - x ;

-- an alternate solution is to use logic that

-- ensures the y=z condition has priority

y_next <=

z when y = z and a = '1' else

y-x when y = z and a = '0' else

y-1 ; -- if y /= z

```