# A 980µW 5.2dB-NF Current-Reused Direct-Conversion Bluetooth-Low-Energy Receiver in 40nm CMOS

Amir H. Masnadi Shirazi<sup>1,2</sup>, Hossein Miri Lavasani<sup>1</sup>, Mojtaba Sharifzadeh<sup>1</sup>, Yashar Rajavi<sup>1</sup>, Shahriar Mirabbasi<sup>2</sup>, and Mazhareddin Taghivand<sup>1</sup>

<sup>1</sup>Qulacomm Inc., San Jose, California; <sup>2</sup>University of British Columbia, Vancouver, Canada

Abstract—This work presents a 980 $\mu$ W direct-conversion BLE receiver at a 1V supply, employing current-reuse and subthreshold techniques. The receiver has a measured noise figure of 5.2dB, integrated from 10kHz to 1MHz, that corresponds to a sensitivity of -95.8dBm. At a receiver gain of 47dB, an IIP3 of -19.7dBm has been measured. The LO integrated phase noise at 2.4GHz is 0.83° with LO spot phase noise of -119.9dBc/Hz at 3MHz frequency offset. The PLL is compacted inside the VCO inductor and has LC-VCO with a tuning range of 4.55GHz to 5.15GHz. Multiple  $\mu$ W-level feedback control loops are used in the design to make it robust over PVT variation. The prototype is implemented in a 40nm LP CMOS process occupying a silicon area of 0.7mm<sup>2</sup>. To the best of our knowledge, the proposed receiver achieves the highest reported figure of merit among the BLE receivers published in the literature.

*Index Terms*— Low power Wireless, Subthreshold, Current-Reuse, Bluetooth Low Energy, CMOS, receiver

## I. INTRODUCTION

Ultra-low-power wireless communication is one of the key enabling technologies for many smart networking applications including Internet of Things (IoT). Over the past decade, Bluetooth Low Energy® (BLE) has been one of the most popular standards for such low-power wireless systems [1]-[4]. To deliver a low power solution, most BLE transceivers trade off power consumption with performance. However, by incorporating innovative low-power circuit design techniques, it is possible to drastically reduce the power consumption in today's advanced radio architectures while delivering competitive performance. Current re-use and subthreshold designs in RF blocks are among the most promising techniques used in modern low power radios, most of which not only suffer from performance degradation over process, voltage, and temperature (PVT) but also they are sensitive to the choice of receiver architectures.

Receiver (RX) architectures such as discrete-time (DT) low-IF and continues-time (CT) sliding IF (SIF) have been used for BLE radios [2]-[5]. The low-IF and SIF topologies suffer from a problematic image that should be rejected by power-hungry multi-stage active filters and downconverters (local oscillators and mixers). This results in a high power consumption for receivers which target sensitivities better than -95dBm. There may also be a need to use high-Q off-chip (or on-chip) filters to further reject the image before the front-ends, as multiple local oscillator (LO) frequencies and associated spurs could desensitize the RX through reciprocal mixing. The RF filtering also increases the cost and degrades the noise figure (NF).

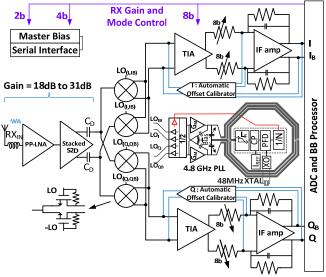

Fig. 1. Block diagram of the proposed ultra-low power direct conversion BLE receiver

This work presents a low power direct conversion receiver (DCR), employing current-reuse and subthreshold designs, with a simple double-frequency VCO that eliminates the intermediate down-conversion steps and the associated circuitry, while achieving sub-mW power consumption. Compared to other RX architectures, the DCR has minimal issues with reciprocal mixing of the LO harmonics and spurs. However, special attention has to be paid to DC-offset and I/Q mismatch issues, both of which call for a fully differential operation [6].

To alleviate these complexities with minimal power penalty, in this paper, a  $980\mu$ W subthreshold current-reused fullydifferential direct-conversion BLE receiver in 40nm CMOS is proposed in which multiple  $\mu$ W-level feedbacks are used to make the design robust over PVT (Fig. 1). The rest of this paper is organized as follows. Section II elaborates on the proposed low-power and high gain LNA. Section III presents the design, implementation, and measured performance of the compact PLL. Section IV discusses the implementation of the baseband amplifier and DC-offset cancellation block. Implementation details, receiver measurement results, and conclusions are provided in Section V and Section VI, respectively.

## 978-1-5090-5191-5/17/\$31.00@2017 IEEE

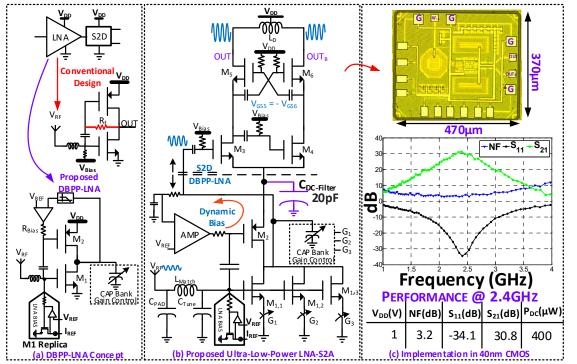

Fig. 2. (a) Block diagram, (b) schematic, and (c) measured standalone performance of the proposed ultra-low-power, PVT robust high gain LNA-S2D

# II. PROPOSED PVT ROBUST LOW POWER LNA

The proposed differential LNA is shown in Fig. 2. The singleended-to-differential (S2D) converter is stacked on top of the LNA to reduce the power consumption. The LNA uses a subtreshold current-reuse push-pull structure (PP-LNA) with a single-inductor input matching network. The effective transconductance of the LNA can be written as  $g_{mp}+g_{mn}$  and hence, as compared to an NMOS-only design, it achieves similar gain with lower power. The push-pull also improves the linearity of the low noise amplifier [7]-[8].

The conventional biasing technique for PP-LNA uses a resistive feedback, namely R<sub>F</sub>, to set the output DC voltage of the LNA to ~ VDD/2 (Fig. 2a). Although using  $R_F$  simplifies the design, in the stacked topology, the output DC voltage varies across PVT which significantly impacts the gain and input matching  $(S_{11})$  of the subthreshold-biased LNA. The proposed dynamic-biased PP-LNA (DBPP-LNA), however, resolves the PVT variation issue by using a dynamically biased feedback loop, which forces the output DC level of the LNA to an adjustable and well-controlled voltage, V<sub>ref</sub> (Fig. 2.a). To perform single-to-differential conversion while increasing the overall gain of the RF front-end, an active S2D converter consisting of two input common-source (CS) buffers followed by a Gm-boosted active balun is used (Fig. 2b). The CS-stages boost the LNA signal and provide a differential V<sub>GS</sub> for M<sub>5</sub> and  $M_6$  ( $V_{GS5} = -V_{GS6}$ ) resulting in negligible amplitude and phase imbalance in the presence of device mismatch. The amplitude mismatch is negligible due to the high gain of the active balun. The L<sub>D</sub> resonates out the capacitance at mixer input node near 2.4GHz allowing the current to flow through the mixer. In addition, to save power, the current of the S2D converter is reused in the LNA by stacking the two stages on top of each other. A 20pF decoupling-cap ( $C_{DC}$ -filer) provides a high frequency AC-short for both the LNA supply and the S2D ground.. The stacked design provides a gain of over 30dB and a NF of less than 3.2dB while consuming 400µW from a 1V supply (Fig. 2c). To properly characterize the LNA-S2D, a separate test structure was designed (Fig. 2c) and measured using RF probes and a vector network analyzer (VNA).

#### III. PROPOSED LOW POWER AND COMPACT PLL

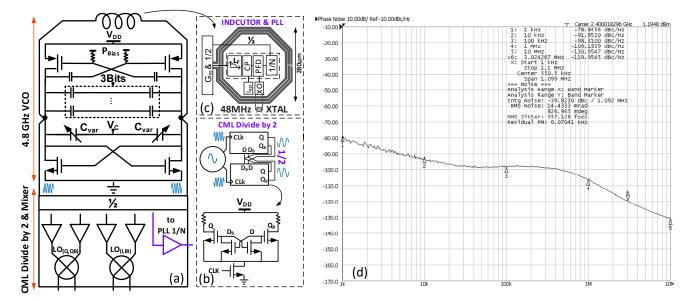

An integer-N PLL operating at twice the carrier frequency is used for downconversion. A CMOS 4.8GHz VCO with programmable PMOS gate-bias is implemented as shown in Fig. 3a. To minimize the VCO power consumption, Q<sub>tank</sub>×L<sub>tank</sub>, that is the product of VCO inductance and its Q, is maximized. The VCO consumes less than 150µW. The VCO has a tuning range of 4.55 GHz to 5.15 GHz. The output frequency of the VCO is divided by two using a quadrature CML divider with resistive load (Fig. 3b). The VCO design was optimized to achieve low phase noise at the offset frequency of 3MHz to alleviate reciprocal mixing of the interferers in the adjacent channel. To reduce the silicon area, the PLL building blocks are physically placed inside a 3-turn VCO inductor, implemented in the copper ultra-thick metal (UTM), which reduces the Q by 6% according to EM simulations but results in over 8% of total area saving (Fig. 3c). The PLL, including the VCO, consumes 280µW and achieves an integrated phase noise (1kHz to 1MHz) of 0.83° (Fig. 3d) and a spot phase noise of -119.9 dBc/Hz at 3MHz offset. The LO, including the divide by two and the buffers driving the down-converting mixers, consume 230µW.

Fig. 3. Proposed frequency synthesis approach showing (a) VCO and (b) CML divider as well as the (c) block diagram and (d) measured phase noise of the PLL

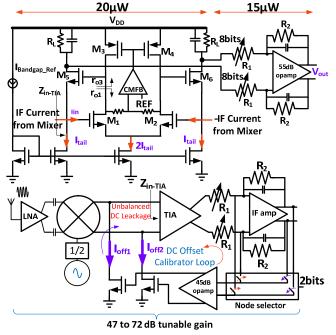

#### IV. PROPOSED LOW-POWER BASEBAND AMPLIFIER

The down-converted current signal is absorbed by a twostage programmable baseband amplifier (Fig. 4). To maximize the absorbption of the input current, a differential regulatedcascode (RGC) transimpedance amplifier (TIA) is employed as the input stage. It can be shown that by using an active load for the proposed TIA (namely M<sub>3</sub> in Fig. 4), the input impedance is independent of bias current, I<sub>tail</sub>, and can be written as:

$$Z_{in-TIA} \approx 1/((r_{o1}||r_{o3}) \times g_{m1}.g_{m5}) \alpha (\lambda_n + \lambda_p) \sqrt{\frac{L_1 L_5}{W_5 W_1}}$$

Where  $g_m$ ,  $r_o$ , and  $\lambda$  are the transconductance, output impedance, and channel-length modulation of transistors.

Fig. 4. Low-power baseband amplifier and automatic offset calibrator

Following the TIA, the second stage is a programmable differential voltage amplifier which employs a tunable shunt-shunt feedback with 12dB of tuning range. The overal baseband gain can be written as:

Gain

$$\approx R_L R_2 / R_1$$

A common-mode feedback loop is included within each differential stage. Input DC offset of the basedband amplifier is a potential concern for the system performance as the DC signal experiences a large gain before reaching the output. To address this issue, an analog DC offset cancellation feedback loop is used in which a sense amplifier balances the output DC levels by injecting a current into the input of the TIA (Fig. 4).

## V. IMPLEMENTATION DETAILS AND MEASUREMENT RESULTS

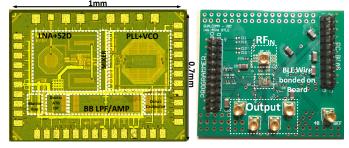

The low power BLE receiver (including the compact all-ininductor PLL) is fabricated in a 40nm LP CMOS process and occupies 0.7mm<sup>2</sup> (Fig. 5). A picture of the test PC board is also shown in Fig. 5.

Fig. 5 Chip micrograph and test board of the proposed BLE receiver.

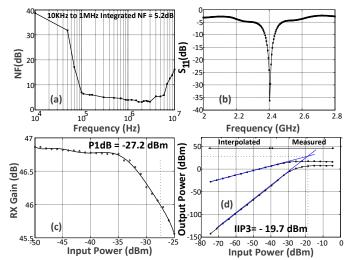

Fig. 6 shows the measured S<sub>11</sub>, NF, and linearity performance of the receiver when consuming 980uA from 1V supply. At 980µW, the receiver achieves a NF of 5.2dB integrated from 10kHz to 1MHz (Fig. 6a) and a sensitivity of –95.8dBm. The LNA shows in-band S<sub>11</sub> < -15dB indicating very good matching to 50 $\Omega$  (Fig. 6b). The gain can be changed from 47dB to 72dB by adjusting the gain of the LNA and baseband amplifier.

Fig. 6. Measured NF, input S11, P1dB, and IIP3 of the BLE receiver

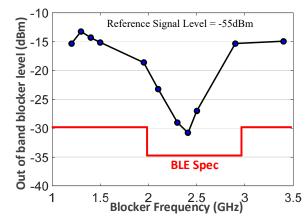

Fig. 7. Blocking performance of proposed BLE receiver

At gain setting of 47dB, the system IIP3 and P1dB are –19.7dBm and -27.2dBm, respectively (Fig. 6c and 6d). The measured blocker performance of the receiver at gain setting of 47dB is shown in Fig. 7. The selectivity of the on-chip matching network of the LNA combined with narrowband nature of the LC tank load of the S2D help reduce the interference to an acceptable limit, meeting the BLE specification. The BLE receiver performance is compared with that of the state-of-the-art BLE radios in Table I. The integration of PLL loop-filter inside the VCO inductor has reduced the total chip area to 0.7mm<sup>2</sup>. The receiver achieves a figure of merit [2] of -95.9dB which is an indication of better sensitivity and lower power consumption compared to published state-of-the-art designs. The design also offers lower NF with comparable linearity and smaller chip area than advanced BLE radios.

## VI. CONCLUSION

A PVT-robust, ultra-low power, and compact direct conversion receiver is presented. It is shown that the proposed DBPP-LNA and stacked S2D can be implemented with sub- $\mu$ W levels while providing high gain at first stage, which further supresses the NF of consecutive stages. To reduce VCO-LNA leakage a compact PLL-in-inductor at twice the input carrier frequency is implemented. The baseband utilises a TIA followed by VGA and uses active DC-offset calibrator, essential for direct conversion receivers. A proof-of-concept prototype 1-Mbps GFSK BLE with configurable gain from 47 to 72dB, is designed and fabricated in a 40nm CMOS LP technology. The receiver achieves a RX sensitivity of -95.8dBm at 980 $\mu$ W with FoM of -95.9, which to the best knowledge of the authors, is the highest reported FoM among the BLE receivers published in literature.

| Reference                   | [1]     | [2]    | [3]    | [4]       | This Work   |

|-----------------------------|---------|--------|--------|-----------|-------------|

| Data Rate &                 | 1-Mbps  | 1-Mbps | 1-Mbps | 1-Mbps    | 1-Mbps      |

| Modulation                  | GFSK    | GFSK   | GFSK   | GFSK      | GFSK        |

| Architecture                | DC      | TD-SIF | TD-SIF | DT-Low IF | DC          |

| Integrated NF (dB)          | N/A     | 6.5    | N/A    | 6.5       | 5.2         |

| RX Gain (dB)                | NA      | NA     | N/A    | 48        | 47-72       |

| RX Sensitivity (dBm)        | -94.5   | -94.5  | -94    | -95       | -95.8       |

| RX IIP3 (dBm)               | N/A     | N/A    | N/A    | -19 @48dB | -19.7 @47dB |

|                             |         |        |        | Gain      | Gain        |

| Integrated PN(°)            | N/A     | N/A    | N/A    | 0.87      | 0.83        |

| PN @ 3MHz                   | N/A     | N/A    | N/A    | N/A       | -119.9      |

| Supply Voltage (V)          | 0.9-3.3 | 1.1    | 1      | 1         | 1           |

| PDC(mW)                     | 11.2    | 6.3    | 3.3    | 2.75      | 0.98        |

| Chip Area(mm <sup>2</sup> ) | 2.9     | 1.1    | 1.3    | 1.84      | 0.7 (RX)    |

| *FoM                        | -84     | -86.5  | -88.8  | -90.1     | -95.9       |

| Technology                  | 55nm    | 40nm   | 40nm   | 28nm      | 40nm        |

|                             | CMOS    | CMOS   | CMOS   | CMOS      | CMOS        |

| Power                       |         |        |        |           |             |

TABLE 1. PERFORMANCE SUMMARY OF STATE-OF-THE BLE RECEIVERS

## ACKNOWLEDGEMENT

We would like to thank Dr. Beomsup Kim for technical support and Dr. Mo Ghahramani for fruitful discussions on the PLL.

## References

[1] J. Prummel et al., "A 10 mW Bluetooth Low-Energy Transceiver With On-Chip Matching,", *IEEE Journal of Solid-State Circuits*, vol. 50, no. 12, pp. 3077-3088, Dec. 2015.

[2] T. Sano *et al.*, "A 6.3mW BLE transceiver embedded RX image-rejection filter and TX harmonic-suppression filter reusing on-chip matching

network," 2015 IEEE International Solid-State Circuits Conference - (ISSCC) ISSCC Dig. Tech, San Francisco, CA, 2015

[3] Y. H. Liu et al., "A 3.7mW-RX 4.4mW-TX fully integrated Bluetooth Low-Energy/IEEE802.15.4/proprietary SoC with an ADPLL-based fast frequency offset compensation in 40nm CMOS," 2015 IEEE International Solid-State Circuits Conference - (ISSCC) Digest of Technical Papers, San Francisco, CA, 2015

[4] F.-W. Kuo, S. Binsfeld Ferreira, M. Babaie, R. Chen, L.-C. Cho, C.-P. Jou, F.-L. Hsueh, G. Huang, I. Madadi, M. Tohidian, and R. B. Staszewski, "A Bluetooth Low-Energy (BLE) transceiver with TX/RX switchable on-chip matching network, 2.75mW high-IF discrete-time receiver, and 3.6mW alldigital transmitter," *Proc. of IEEE Symp. on VLSI Circuits (VLSI)*, sec. 7.1, pp. 64–65, 15 June 2016, Honolulu, HI, USA.

[5] Amir Hossein Masnadi Shirazi, Hooman Rashtian, Reza Molavi, Thierry Taris, Hossein Miri Lavasani, Shahriar Mirabbasi, "On the design of combined LNA-VCO-mixer for low-power and low-voltage CMOS receiver front-ends" Microelectronics Journal, Volume 57, November 2016, Pages 34-47

[6] A. A. Abidi, "Direct-conversion Radio Transceivers for Digital Communications," in *IEEE Journal of Solid-State Circuits*, vol. 30, no. 12, pp. 1399-1410, Dec. 1995

[7]A. Selvakumar, M. Zargham and A. Liscidini, "Sub-mW Current Re-Use Receiver Front-End for Wireless Sensor Network Applications," in *IEEE Journal of Solid-State Circuits*, vol. 50, no. 12, pp. 2965-2974, Dec. 2015

[8] C. T. Fu, H. Lakdawala, S. S. Taylor and K. Soumyanath, "A 2.5GHz 32nm 0.35mm2 3.5dB NF -5dBm P1dB fully differential CMOS push-pull LNA with integrated 34dBm T/R switch and ESD protection," 2011 IEEE International Solid-State Circuits Conference, San Francisco, CA, 2011, pp. 56-58.

<sup>\*</sup> RX Figure of Merit (FoM) =  $RX_{Sensitivity} + 10\log(\frac{Power}{1mW})$