# Vector Processing as a Soft-CPU Accelerator

by

Jason Kwok Kwun Yu

B.A.Sc, Simon Fraser University, 2005

# A THESIS SUBMITTED IN PARTIAL FULFILMENT OF THE REQUIREMENTS FOR THE DEGREE OF

Master of Applied Science

in

The Faculty of Graduate Studies

(Electrical and Computer Engineering)

The University Of British Columbia  ${\it May, 2008}$

© Jason Kwok Kwun Yu 2008

## Abstract

Soft processors simplify hardware design by being able to implement complex control strategies using software. However, they are not fast enough for many intensive data-processing tasks, such as highly data-parallel embedded applications. This thesis suggests adding a vector processing core to the soft processor as a general-purpose accelerator for these types of applications. The approach has the benefits of a purely software-oriented development model, a fixed ISA allowing parallel software and hardware development, a single accelerator that can accelerate multiple functions in an application, and scalable performance with a single source code. With no hardware design experience needed, a software programmer can make area-versusperformance tradeoffs by scaling the number of functional units and register file bandwidth with a single parameter. The soft vector processor can be further customized by a number of secondary parameters to add and remove features for the specific application to optimize resource utilization. This thesis shows that a vector processing architecture maps efficiently into an FPGA and provides a scalable amount of performance for a reasonable amount of area. Configurations of the soft vector processor with different performance levels are estimated to achieve speedups of 2-24× for 5-26× the area of a Nios II/s processor on three benchmark kernels.

# Table of Contents

| A            | bstra  | et                                                                                                                                | iii |

|--------------|--------|-----------------------------------------------------------------------------------------------------------------------------------|-----|

| Ta           | able ( | f Contents                                                                                                                        | V   |

| Li           | ist of | Tables                                                                                                                            | xi  |

| Li           | ist of | Figures                                                                                                                           | iii |

| $\mathbf{A}$ | ckno   | vledgments                                                                                                                        | XV  |

| 1            | Intr   | $\mathbf{oduction}  \dots $ | 1   |

|              | 1.1    | Motivation                                                                                                                        | 3   |

|              | 1.2    | Contributions                                                                                                                     | 5   |

|              | 1.3    | Thesis Outline                                                                                                                    | 6   |

| <b>2</b>     | Bac    | ground                                                                                                                            | 7   |

|              | 2.1    | Vector Processing Overview                                                                                                        | 7   |

|              |        | 2.1.1 Exploiting Data-level Parallelism                                                                                           | 8   |

|              |        | 2.1.2 Vector Instruction Set Architecture                                                                                         | 10  |

|              |        | 2.1.3 Microarchitectural Advantages of Vector Processing                                                                          | 11  |

|              | 2.2    | Vector Processors and SIMD Extensions                                                                                             | 12  |

|              |        | 2.2.1 SIMD Extensions                                                                                                             | 12  |

|              |        | 2.2.2 Single-chip Vector Processors                                                                                               | 13  |

### Table of Contents

|   |     | 2.2.3   | FPGA-based Vector Processors                   |

|---|-----|---------|------------------------------------------------|

|   | 2.3 | Multip  | processor Systems                              |

|   | 2.4 | Custo   | m-designed Hardware Accelerators               |

|   |     | 2.4.1   | Decoupled Co-processor Accelerators            |

|   |     | 2.4.2   | Custom Instruction Accelerators                |

|   | 2.5 | Synthe  | esized Hardware Accelerators                   |

|   |     | 2.5.1   | C-based Synthesis                              |

|   |     | 2.5.2   | Block-based Synthesis                          |

|   |     | 2.5.3   | Application Specific Instruction Set Processor |

|   |     | 2.5.4   | Synthesis from Binary Decompilation            |

|   | 2.6 | Other   | Soft Processor Architectures                   |

|   |     | 2.6.1   | Mitrion Virtual Processor                      |

|   |     | 2.6.2   | VLIW Processors                                |

|   |     | 2.6.3   | Superscalar Processors                         |

|   | 2.7 | Summ    | ary 31                                         |

| 3 | Con | nfigura | ble Soft Vector Processor                      |

|   | 3.1 | Requi   | rements                                        |

|   | 3.2 | Soft V  | Tector Architecture                            |

|   |     | 3.2.1   | System Overview                                |

|   |     | 3.2.2   | Hybrid Vector-SIMD Model                       |

|   | 3.3 | Vector  | Lane Datapath                                  |

|   |     | 3.3.1   | Vector Pipeline                                |

|   |     | 3.3.2   | Datapath Functional Units                      |

|   |     | 3.3.3   | Distributed Vector Register File               |

|   |     | 3.3.4   | Load Store Unit                                |

|   |     | 3.3.5   | Local Memory                                   |

|   | 3.4  | Memo                                   | ry Unit                                             | 41 |

|---|------|----------------------------------------|-----------------------------------------------------|----|

|   |      | 3.4.1                                  | Load Store Controller                               | 42 |

|   |      | 3.4.2                                  | Read Interface                                      | 42 |

|   |      | 3.4.3                                  | Write Interface                                     | 43 |

|   | 3.5  | FPGA                                   | -Specific Vector Extensions                         | 45 |

|   | 3.6  | Config                                 | gurable Parameters                                  | 47 |

|   | 3.7  | Design                                 | Flow                                                | 48 |

|   |      | 3.7.1                                  | Soft Vector Processor Flow versus C-based Synthesis | 48 |

|   |      | 3.7.2                                  | Comment on Vectorizing Compilers                    | 50 |

| 4 | Res  | ulte                                   |                                                     | 51 |

| 4 |      |                                        |                                                     |    |

|   | 4.1  |                                        | mark Suite                                          |    |

|   | 4.2  | Bench                                  | mark Preparation                                    |    |

|   |      | 4.2.1                                  | General Methodology                                 | 54 |

|   |      | 4.2.2                                  | Benchmark Vectorization                             | 54 |

|   |      | 4.2.3                                  | Benchmark Tuning for C2H Compiler                   | 59 |

|   |      | 4.2.4                                  | Soft Vector Processor Per Benchmark Configuration   | 60 |

|   | 4.3  | Resou                                  | rce Utilization Results                             | 60 |

|   | 4.4  | Perfor                                 | mance Results                                       | 63 |

|   |      | 4.4.1                                  | Performance Models                                  | 64 |

|   |      | 4.4.2                                  | RTL Model Performance                               | 66 |

|   |      | 4.4.3                                  | Ideal Vector Model                                  | 68 |

|   |      | 4.4.4                                  | C2H Accelerator Results                             | 70 |

|   |      | 4.4.5                                  | Vector versus C2H                                   | 71 |

| 5 | Con  | chisio                                 | ns and Future Work                                  | 7: |

| J |      |                                        |                                                     |    |

|   | Ð. I | F1111111111111111111111111111111111111 | e Work                                              | 75 |

### Table of Contents

| Bi               | bliog | raphy  |                                                | 79 |

|------------------|-------|--------|------------------------------------------------|----|

| $\mathbf{A}_{]}$ | ppen  | dices  |                                                |    |

| $\mathbf{A}$     | Soft  | Vecto  | or Processor ISA                               | 35 |

|                  | A.1   | Introd | $\operatorname{uction}$                        | 35 |

|                  |       | A.1.1  | Configurable Architecture                      | 36 |

|                  |       | A.1.2  | Memory Consistency                             | 37 |

|                  | A.2   | Vector | Register Set                                   | 37 |

|                  |       | A.2.1  | Vector Registers                               | 37 |

|                  |       | A.2.2  | Vector Scalar Registers                        | 38 |

|                  |       | A.2.3  | Vector Flag Registers                          | 38 |

|                  |       | A.2.4  | Vector Control Registers                       | 39 |

|                  |       | A.2.5  | Multiply-Accumulators for Vector Sum Reduction | 90 |

|                  |       | A.2.6  | Vector Lane Local Memory                       | 90 |

|                  | A.3   | Instru | ction Set                                      | 92 |

|                  |       | A.3.1  | Data Types                                     | 92 |

|                  |       | A.3.2  | Addressing Modes                               | 92 |

|                  |       | A.3.3  | Flag Register Use                              | 92 |

|                  |       | A.3.4  | Instructions                                   | 92 |

|                  | A.4   | Instru | ction Set Reference                            | 93 |

|                  |       | A.4.1  | Integer Instructions                           | 93 |

|                  |       | A.4.2  | Logical Instructions                           | 96 |

|                  |       | A.4.3  | Fixed-Point Instructions (Future Extension)    | 96 |

|                  |       | A.4.4  | Memory Instructions                            | 99 |

|                  |       | A.4.5  | Vector Processing Instructions                 | )2 |

|                  |       | A.4.6  | Vector Flag Processing Instructions            | )5 |

|     | A.4.7  | Miscellaneous Instructions                     |

|-----|--------|------------------------------------------------|

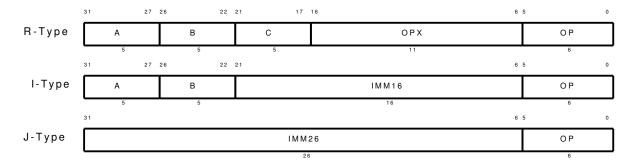

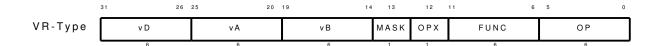

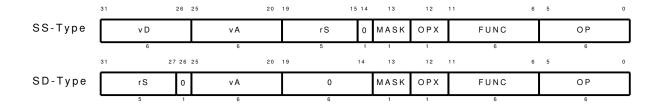

| A.5 | Instru | ction Formats                                  |

|     | A.5.1  | Vector Register and Vector Scalar Instructions |

|     | A.5.2  | Vector Memory Instructions                     |

|     | A.5.3  | Instruction Encoding                           |

# List of Tables

| 1.1  | New soft vector processor instruction extensions                               | 6   |

|------|--------------------------------------------------------------------------------|-----|

| 2.1  | Partial list of FPGA-based multiprocessor systems in literature                | 17  |

| 3.1  | List of configurable processor parameters                                      | 48  |

| 4.1  | Per benchmark soft vector processor configuration parameter settings           | 60  |

| 4.2  | Resource usage of vector processor and C2H accelerator configurations          | 61  |

| 4.3  | Resource usage of vector processor when varying $NLane$ and $MemMinWidth$ with |     |

|      | 128-bit $MemWidth$ and otherwise full features                                 | 62  |

| 4.4  | Resource utilization from varying secondary processor parameters               | 63  |

| 4.5  | Ideal vector performance model                                                 | 65  |

| 4.6  | Performance measurements                                                       | 67  |

| A.1  | List of configurable processor parameters                                      | 87  |

| A.2  | List of vector flag registers                                                  | 88  |

| A.3  | List of control registers                                                      | 89  |

| A.4  | Instruction qualifiers                                                         | 93  |

| A.11 | Nios II Opcode Usage                                                           | .07 |

| A.12 | Scalar register usage as source or destination register                        | .08 |

| A.13 | Vector register instruction function field encoding (OPX=0)                    | .09 |

| A.14 | Scalar-vector instruction function field encoding (OPX=1)                      | 10  |

| A.15 | Fixed-point instruction function field encoding (OPX=0)                        | 10  |

### List of Tables

| A.16 Flag and miscellaneous instruction function field encoding (OPX=1) $\ \ldots \ \ldots \ \ldots$ | 111 |

|------------------------------------------------------------------------------------------------------|-----|

| A.17 Memory instruction function field encoding                                                      | 111 |

# List of Figures

| 2.1 | 8-tap FIR filter MIPS assembly                                                     | 9  |

|-----|------------------------------------------------------------------------------------|----|

| 2.2 | 8-tap FIR filter VIRAM vector assembly                                             | 10 |

| 2.3 | Nios II custom instruction formats                                                 | 19 |

| 2.4 | Example Nios II system with C2H accelerators                                       | 22 |

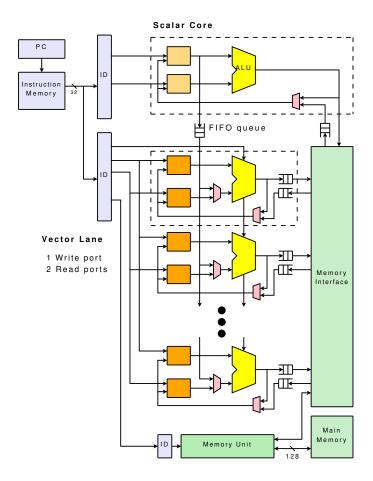

| 3.1 | Scalar and vector core interaction                                                 | 35 |

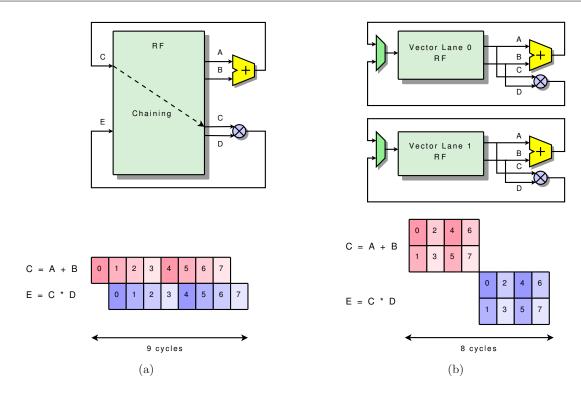

| 3.2 | Vector chaining versus hybrid vector-SIMD execution                                | 36 |

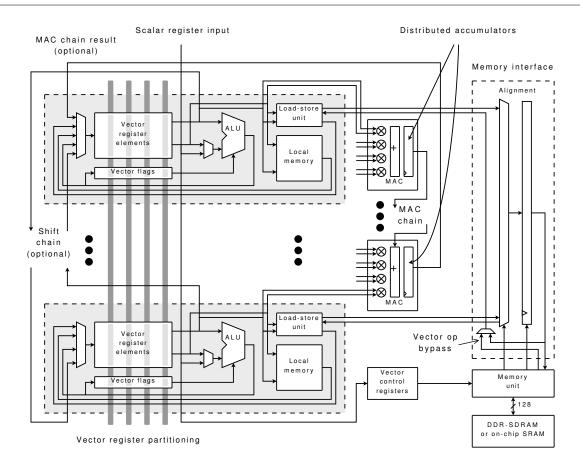

| 3.3 | Vector co-processor system block diagram                                           | 38 |

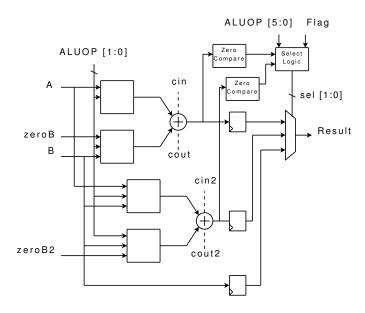

| 3.4 | Vector Lane ALU                                                                    | 39 |

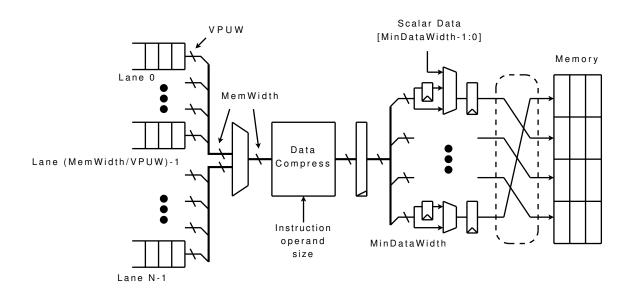

| 3.5 | Soft vector processor write interface                                              | 43 |

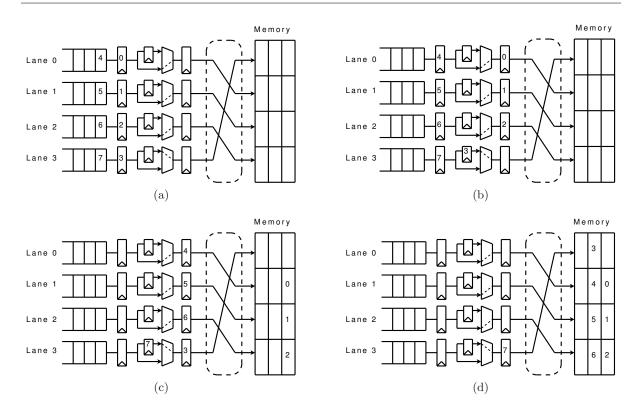

| 3.6 | Data alignment using crossbar and delay network for vector store                   | 44 |

| 3.7 | 8-tap FIR filter vector assembly                                                   | 47 |

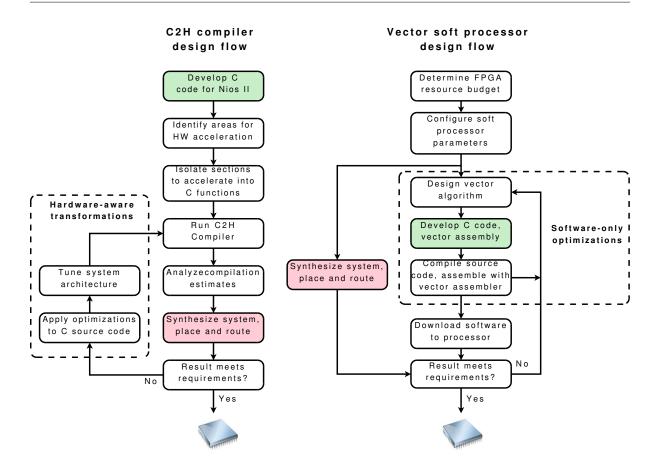

| 3.8 | Altera C2H compiler design flow versus soft vector processor design flow           | 49 |

| 4.1 | Motion estimation C code                                                           | 52 |

| 4.2 | $5\times 5$ median filter C code                                                   | 53 |

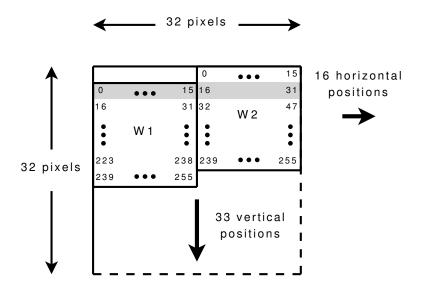

| 4.3 | Simultaneously matching two copies of the macroblock to a reference frame          | 55 |

| 4.4 | Code segment from the motion estimation vector assembly. The code to handle        |    |

|     | the first and last rows of the windows are not shown                               | 56 |

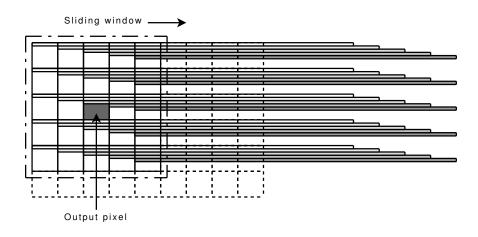

| 4.5 | Vectorizing the image median filter                                                | 57 |

| 4.6 | Median filter inner loop vector assembly                                           | 57 |

| 4.7 | Vector assembly for loading AES data and performing AES encryption round $$ . $$ . | 58 |

## List of Figures

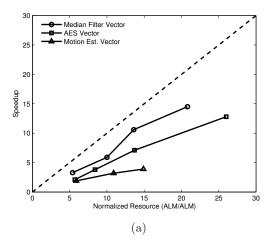

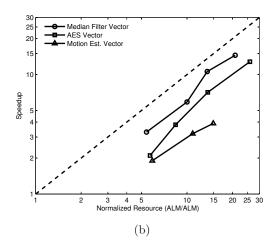

| 4.8 | RTL Model speedup over Ideal Nios Model                               | 68 |

|-----|-----------------------------------------------------------------------|----|

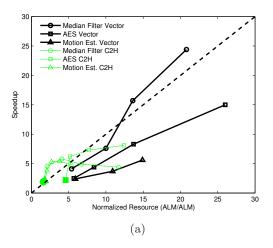

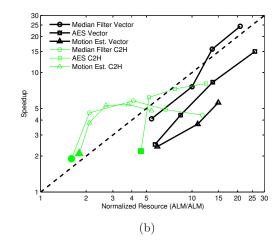

| 4.9 | Ideal Vector Model and C2H Model speedup over Ideal Nios Model        | 69 |

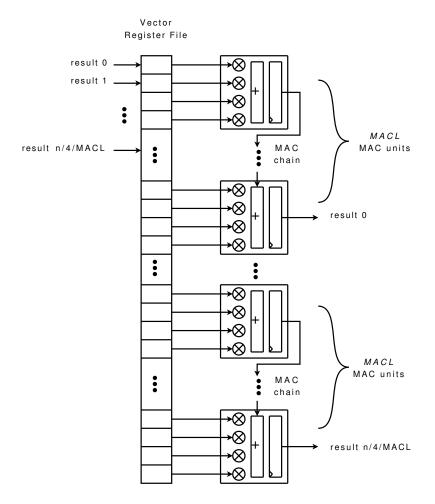

| A.1 | Connection between distributed MAC units and the vector register file | 91 |

# Acknowledgments

Foremost I would like to thank my supervisor Dr. Guy Lemieux for teaching me the many aspects of academic research, and for his guidance and support throughout my research project. The many hours you spent proofreading my conference papers and thesis are very much appreciated.

Thanks to Blair Fort for providing the UTHe processor used in this research, without which this project would have taken much longer.

I would like to thank my friends in the SoC lab and throughout the department, on the ECEGSA executive, and in the faculty music group for making my graduate life at UBC enjoyable, and allowing me to develop both academically and personally during my life at UBC.

Finally, I would like to thank my loving family and dear Florence for their constant support and encouragement.

## Chapter 1

# Introduction

Advanced signal processing algorithms and large volumes of multimedia data in many embedded applications today demand high performance embedded systems. These systems rely on programmable microprocessors, digital signal processors (DSPs), or field-programmable gate arrays (FPGAs) to do intensive computations. Designing embedded systems using these platforms requires expertise in both hardware and software, and is increasingly becoming a challenge due to increasing complexity and performance requirements of today's applications. A high performance platform that is also easy to use and reduces time to market is needed to address these challenges, and an effective FPGA-based soft processor platform is one possible solution.

FPGAs are a specialized type of integrated circuit (IC) that can be programmed and reprogrammed by the user after fabrication to implement any digital circuit. FPGAs achieve this reconfigurability through the use of flexible lookup tables and routing connections that are configured by a user-downloaded bitstream. There are a number of advantages to using FPGAs in embedded systems. Manufacturing a set of masks to fabricate application specific integrated circuits (ASICs) such as most microprocessors and DSPs costs millions of dollars in today's advanced fabrication technologies. The design, fabrication, and validation steps needed to produce an ASIC is a lengthy process with a long turnaround time, and mistakes found after fabrication require a new set of masks to correct and are thus very costly. These high non-recurring engineering costs (NRE) make ASICs only practical for devices with sufficiently large market and volume. FPGAs, on the other hand, can be purchased off the shelf with a low up-front cost. The devices have been pre-tested by the FPGA vendor and are guaranteed to function correctly. The reconfigurable nature allows users to quickly iterate their designs

during development, speeding up time to market. Even in the final product, reconfigurability can allow the system firmware to be updated to take advantage of new firmware features or to adhere to new standards. A single FPGA can also replace multiple components in a system that would have required separate ICs, again reducing cost.

From a performance perspective, FPGAs are generally considered lower performance than ASICs due to a lower maximum clock speed. Nonetheless, FPGAs are capable of tremendous raw processing power. The reconfigurable lookup tables of an FPGA form one large computational fabric that is able to perform many operations in parallel, and the large number of embedded on-chip memories can provide tremendous on-chip memory bandwidth. Consider the largest Altera Stratix III FPGA, EP3SL340, which has approximately 135,000 adaptive logic modules (ALMs). Each ALM is able to compute a one-bit function of up to six inputs per clock cycle or implement up to two three-bit adders [1]. Taking the adders alone, if they can be fully utilized, is equivalent to almost 8,440 three-input 32-bit adders. In comparison, many low-cost microprocessors in embedded systems have only one two-input adder in a single arithmetic logic unit (ALU).

Using FPGAs has traditionally required specialized hardware design knowledge and familiarity with a hardware description language (HDL) such as the VHSIC (Very High Speed Integrated Circuit) Hardware Description Language (VHDL) or Verilog in order to implement the desired circuitry. The introduction of embedded processor cores into FPGAs, both as hard cores that are implemented in silicon like the rest of the FPGA circuitry, and as soft cores that are synthesized and then programmed on to the FPGA like other user designs, has simplified the design process and technical requirement of using FPGAs. According to a survey conducted in 2007 [2], 36% of respondants used a processor (either hard or soft core) inside the FPGA in their embedded designs, and this figure had increased from 33% in 2006, and 32% in 2005. Embedded software developers can now program in a high-level language such as C or C++, and compile their programs to run on the embedded processor core within the FPGA. This combination of embedded processor core and programmable logic has also opened up the

possibility of implementing custom hardware circuitry in the programmable logic to interact with the processor core.

#### 1.1 Motivation

More and more embedded systems today target multimedia, signal processing, and other computationally intensive workloads. These applications typically have a relatively small set of operations that have to be repeatedly performed over a large volume of data. This form of parallelism is referred to as data-level parallelism. Current soft processors designed for FPGAs such as Nios II [3] by Altera and MicroBlaze [4] by Xilinx frequently do not deliver enough computational power to achieve the desired performance in these workloads. These soft processors have only a single ALU and can only perform one computation per clock cycle. Although they come in a few performance levels that successively add more advanced and complex architectural features, even the highest performing core is frequently insufficient to handle the intensive processing tasks.

Many solutions have been proposed in both commercial and academic spaces to improve the performance of soft core processors on FPGAs. They can be largely categorized into four categories: multiprocessor systems, custom-designed hardware accelerators, synthesized hardware accelerators, and other soft processor architectures. Multiprocessor systems contain multiple processor cores, and rely upon shared memory or message passing to communicate and synchronize. They generally require parallel programming knowledge from the user, and as a result are more difficult to program and use. Hardware accelerators utilize the programmable logic of an FPGA to implement dedicated accelerators for processing certain functions. Custom-designed hardware accelerators have to be designed by the user in HDL, but the FPGA development tools may provide an automated way to connect the accelerator to the processor core once it has been designed. They still require the user to design hardware, and verify and test the accelerator in hardware to ensure correct operation. Synthesized hardware accelerators are

automatically synthesized from a high-level language description or from a visual representation of the function to be accelerated. The major improvement is that users can use hardware accelerators without knowledge of an HDL, and with little or no knowledge of hardware design.

An improved soft processor architecture has the benefit of a purely software solution, requiring no hardware design or synthesis effort from the user. Depending on the complexity of the programming model of the architecture, it can allow users to improve performance of their applications with minimal learning curve. A soft processor also provides a specification across hardware and software (in the form of a fixed instruction set architecture) that does not change throughout the design cycle, allowing hardware and software development to proceed in parallel.

Some common processor architectures have already been implemented in FPGAs. Very Long Instruction Word (VLIW) architectures have been proposed for soft processors on FPGAs, and superscalar architectures have also been attempted, but neither of them map efficiently to the FPGA architecture, bloating resource usage and introducing unnecessary bottlenecks in performance. To improve performance of data-parallel embedded applications on soft processor systems, it is imperative to take advantage of the parallelism in the hardware. Given the pure software advantage of using an improved soft processor architecture, an ideal solution would be a processor architecture that is inherently parallel, and maps well to the FPGA architecture.

The solution proposed by this thesis is a soft processor tailored to FPGAs based on a vector processor architecture. A vector processor is capable of high performance in data-parallel embedded workloads. Kozyrakis [5] studied the vectorizability of the 10 consumer and telecommunications benchmarks in the EEMBC suite using the VIRAM [6] compiler, and found the average vector length of the benchmarks ranged from 13 to 128 (128 is the maximum vector length supported by VIRAM). The study shows that many embedded applications are vectorizable to long vector lengths, allowing significant performance improvements using vector processing. Vector processing also satisfies the requirements of a parallel architecture, and can be implemented efficiently in FPGAs, as will be shown in this thesis.

### 1.2 Contributions

The main contribution of this research is applying vector processing, an inherently parallel programming model, to the architecture of soft core processors to improve their performance on data-parallel embedded applications. A soft vector processor provides scalable and user-selectable amount of acceleration and resource usage, and a configurable feature set, in a single application-independent accelerator that requires zero hardware design knowledge or effort from the user. The scalability of vector processoring allows users to make large performance and resource tradeoffs in the vector processor with little or no modification to software. A soft vector processor can further exploit the configurability of FPGAs by customizing the feature set and instruction support of the processor to the target application. Customization extends even to a configurable vector memory interface that can implement a memory system tailored to the application. This makes accessible to the user a much larger design space and larger possible tradeoffs than current soft processor solutions. The application-independent architecture of the vector processor allows a single accelerator to accelerate multiple sections of an application and multiple applications.

As part of this research, a complete soft vector processor was implemented in Verilog targetting an Altera Stratix III FPGA to illustrate the feasibility of the approach and possible performance gains. The processor adopts the VIRAM instruction set architecture (ISA), but makes modifications to tailor the ISA features to FPGAs. A novel instruction execution model that is a hybrid between traditional vector and single-instruction-multiple-data (SIMD) is used in the processor. This work also identifies three ways traditional vector processor architectures can be adapted to better exploit features of FPGAs:

- 1. Use of a partitioned register file to scale bandwidth and reduce complexity,

- 2. Use of multiply-accumulate (MAC) units for vector reduction,

- 3. Use of a local memory in each vector lane for lookup-table functions.

Table 1.1 lists new instructions that are added to the soft vector processor instruction set

Table 1.1: New soft vector processor instruction extensions

| Instruction | Description                             |

|-------------|-----------------------------------------|

| vmac        | Multiply-accumulate                     |

| vcczacc     | Compress copy from accumulator and zero |

| vldl        | Load from local memory                  |

| vstl        | Store to local memory                   |

| veshift     | Vector element shift                    |

| vabsdiff    | Vector absolute difference              |

to support new features that did not exist in VIRAM.

### 1.3 Thesis Outline

The remainder of the thesis is organized as follows. Chapter 2 gives an overview of vector processing and previously implemented vector processors, and describes other solutions to accelerate applications on soft processor systems, highlighting their advantages and limitations. Chapter 3 describes in detail the architecture of the soft vector processor and its extensions to traditional vector architectures. Chapter 4 provides experimental results illustrating the strengths of the soft vector processor compared to a recent commercial solution in the synthesized accelerator category. Finally, Chapter 5 summarizes the work in this thesis and provides suggestions for future work.

## Chapter 2

# Background

This chapter provides background on vector processing and application acceleration for soft processor-based systems in FPGAs. First, an overview of how vector processing accelerates data-parallel computations is presented, followed by a discussion of previously implemented vector processors. The remainder of the chapter surveys other current solutions for improving the performance of soft processors and accelerating FPGA-based applications. A representative set of academic and commercial tools are described according to the four categories introduced in Chapter 1: multiprocessor systems, custom-designed hardware accelerators, synthesized accelerators, and other soft processor architectures.

### 2.1 Vector Processing Overview

Vector processing has been in use in supercomputers for scientific tasks for over two decades. As semiconductor technology improved, single-chip vector processors have become possible, and recent supercomputing systems like the Earth Simulator [7] and Cray X1 are based on such single-chip vector processors. The next sections will give an overview of how vector processing can accelerate data-parallel computations, and the characteristics of a vector instruction set, with the goal of demonstrating that vector processing is a suitable model for soft processor acceleration.

#### 2.1.1 Exploiting Data-level Parallelism

The vector processing model operates on vectors of data. Each vector operation specifies an identical operation on the individual data elements of the source vectors, producing an equal number of independent results. Being able to specify a single operation on multiple data elements makes vector processing a natural method to exploit data-level parallelism, which has the same properties. The parallelism captured by vector operations can be exploited by vector processors in the form of multiple parallel datapaths—called *vector lanes*—to reduce the time needed to execute each vector operation.

To illustrate the vector processing programming model, consider an 8-tap finite impulse response (FIR) filter

$$y[n] = \sum_{k=0}^{7} x[n-k]h[k],$$

which can be implemented in MIPS asembly code as shown in Figure 2.1. The code segment contains one inner loop to perform multiply-accumulate on the data buffer and filter coefficients, and an outer loop to demonstrate processing multiple new data samples. In a real application, the outer loop will iterate as long as there are new inputs to be filtered. The inner loop iterates 8 times for the 8-tap filter. Adding the 10 instructions in the outer loop (assuming branch taken on line 17) gives a total of 74 instructions per result.

The same FIR filter implemented in VIRAM vector code is shown in Figure 2.2. The vector processor extracts data-level parallelism in the multiplication operation by multiplying all the coefficients and data samples in parallel. One common operation in vector processing is reduction of the data elements in a vector register. In the FIR filter example, the multiplication products need to be sum-reduced to the final result. The vhalf instruction facilitates reduction of data elements by extracting the lower half of a vector register to the top of a destination vector register. A total of log(VL) vhalf and add instructions are needed to reduce the entire vector. In the vector code, the filter coefficients and previous data samples are kept in vector registers when a new data sample is read to reduce the number of memory accesses. Line 15

```

.L10:

; Loop while new inputs received

; Zero sum

r6, zero

mov

; Load address of sample buffer

mov

r4, sp

r5, 8

; Set number of taps

movi

.L8:

5

ldw

r12, 0(r4)

; Load data from buffer

r3, 100(r4)

; Load coefficient

ldw

r5, r5, -1

addi

addi

r4, r4, 4

mul

r2, r12, r3

; Multiply

10

add

r6, r6, r2

; Accumulate

r5, zero, .L8

bne

r6. 0(r9)

: Store filter result

stw

r11, 0(r7)

; Store new sample to buffer

stw

15

addi

r7, r7, 4

; Increment buffer position

bgeu

r10, r7, .L4

; Check for end of buffer

r7, sp

; Reset new sample pointer

mov

.L4:

r8, r8, -1

addi

20

r9, r9, 4

addi

bne

r8, zero, .L10

```

Figure 2.1: 8-tap FIR filter MIPS assembly

to 21 of Figure 2.2 stores the reduced result to memory, shifts the filter data elements by one position using a vector extract opertaion to align them with the coefficients, and copies a new data element from the scalar core. A total of 18 instructions are needed to calculate a single result. The capitalized instructions are specific to the VIRAM implementation of the FIR filter, and can be compared to Figure 3.7 for differences between the VIRAM and soft vector processor implementations.

The vector code has a significant advantage over the MIPS code in terms of the number of instructions executed. Scaling the FIR filter example to 64 filter taps, the MIPS code would require executing 522 instructions, while the vector code would still only execute 18 instructions, but have a different value of VL.

|      | vmstc            | vbase0, sp    | ; Load base address                       |    |

|------|------------------|---------------|-------------------------------------------|----|

|      | ${ m vmstc}$     | vbase1, r3    | ; Load coefficient address                |    |

|      | $\mathrm{vmstc}$ | VL, r2        | ; Set VL to num taps                      |    |

|      | vld.h            | v2, vbase1    | ; Load filter coefficients                |    |

|      | vld.h            | v1, vbase0    | ; Load input vector                       | 5  |

| .L5: |                  | ,             | , 1                                       |    |

|      | VMULLO.VV        | v3, v0, v2    | ; Multiply data and coefficients          |    |

|      | VHALF            | v4, v3        | ; Extract half of the vector              |    |

|      | VADD.VV          | v3, v4, v3    | ; VL is automatically halved by vhalf     |    |

|      |                  | v4, v3        |                                           | 10 |

|      |                  | v3, v4, v3    |                                           |    |

|      |                  | v4, v3        | ; 3 half—reductions for 8 taps            |    |

|      | VADD.VV          | v3, v4, v3    | ,                                         |    |

|      | $\mathrm{vmstc}$ | VL, r9        | ; Reset VL to num taps (vhalf changes VL) |    |

|      |                  | . , -         | ,,                                        | 15 |

|      | $\mathrm{vmstc}$ | vindex, r8    | ; Set vindex to 0                         |    |

|      | vext.vs          | r10, v3       | ; Extract final summation result          |    |

|      | stw              | r10, 0(r4)    | ; Store result                            |    |

|      | VMSTC            | vindex, r7    |                                           |    |

|      | VEXT.VV          | v1, v1        | ; Shift vector up 1                       | 20 |

|      | vmstc            | vindex, r6    | ; Set vindex to NTAP-1                    | 20 |

|      | vins.vs          | v1, r5        | ; Insert new sample                       |    |

|      | addi             | r3, r3, -1    | , moere new sample                        |    |

|      | addi             | r4, r4, 4     |                                           |    |

|      | bne              | r3, zero, .L5 |                                           | 25 |

|      | DHE              | 15, Ze10, .L3 |                                           | 25 |

|      |                  |               |                                           |    |

Figure 2.2: 8-tap FIR filter VIRAM vector assembly

#### 2.1.2 Vector Instruction Set Architecture

Vector instructions are a compact way to encode large amounts of data parallelism, each specifying tens of operations and producing tens of results at a time. Modern vector processors like the Cray X1 use a register-register architecture similar to RISC processors [8]. Source operands are stored in a large vector register file that can hold a moderate number of vector registers, each containing a large number of data elements.

A vector architecture contains a vector unit and a separate scalar unit. The scalar unit is needed to execute non-vectorizable portions of the code, and most control flow instructions. In many vector instruction sets, instructions that require both vector and scalar operands, such as adding a constant to a vector, also read from the scalar unit. Vector addressing modes can efficiently gather and scatter entire vectors to and from memory. The three primary vector addressing modes are: unit stride, constant stride, and indexed addressing. Unit stride accesses data elements in adjacent memory locations, constant stride accesses data elements in memory with a constant size separation between elements, and indexed addressing accesses data elements by adding a variable offset for each element to a common base address.

Vector instructions are controlled by a vector length (VL) register, which specifies the number of elements within the vector to operate on. This vector length register can be modified on a per-instruction basis. A common method to implement conditional execution is using vector flag registers as an execution mask. In this scheme, a number of vector flag registers are defined in addition to the vector registers, and have the same vector length such that one bit in the vector flag register is associated with each data element. Depending on this one bit value, the operation on the data element will be conditionally executed. Some instructions use the flag register slightly differently. For example the vector merge instruction uses the bit value in the flag register to choose between two source registers.

Besides inter-vector operations, vector instruction sets also support intra-vector operations that manipulate data elements within a vector. Implementing these instructions are, however, tricky, as they generally require inter-lane communication due to partitioning of data elements over multiple lanes. For example, the VIRAM instruction set implements a number of instructions like vhalf, vhalfup, and vhalfdn to support element permutations.

### 2.1.3 Microarchitectural Advantages of Vector Processing

The previous sections have already illustrated the ease-of-use and instruction set efficiency of the vector programming model. Vector processing also has many advantages that simplify the vector processor microarchitecture. Vector instructions alleviate bottlenecks in instruction issue by specifying and scheduling tens of operations, which occupy the processor for many cycles at a time. This reduces instruction bandwidth needed to keep the functional units busy [9]. Vector instructions also ease dependency checking between instructions, as the data elements within a vector instruction are guaranteed to be independent, so each vector instruction only needs to be checked once for dependencies before issuing. By replacing entire loops, vector instructions eliminate loop control hazards. Finally, vector memory accesses are effective against the ever-increasing latency to main memory, as they are able to amortize the penalty over the many accesses made in a single memory instruction. This makes moderate-latency, high-throughput memory technologies such as DDR-SDRAM good candidates for implementing main memory for vector processors.

### 2.2 Vector Processors and SIMD Extensions

Having discussed the merits of vector processing, the following sections will describe a number of single-chip and FPGA-based vector processors in literature, and briefly explain processors based on vector-inspired SIMD processing. SIMD processing is a more limited form of the vector computing model. The most well-known usage of SIMD processing is in multimedia instruction extensions common in mainstream microprocessors. Recent microprocessors from Intel, IBM, and some MIPS processors all support SIMD extensions.

#### 2.2.1 SIMD Extensions

SIMD extensions such as Intel SSE and PowerPC AltiVec are oriented towards short vectors. Vector registers are typically 128 bits wide for storing an entire vector. The data width is configurable from 8 to 32 bits, allowing vector lengths to range from 16 (8 bits) to 4 (32 bits). SIMD instructions operate on short, fixed-length vectors, and each instruction typically executes in a single cycle. In contrast, vector architectures have a vector length register that can be used to modify the vector length during runtime, and one vector instruction can process a long vector over multiple cycles. In general, SIMD extensions lack support for strided memory access patterns and more complex memory manipulation instructions, hence they must devote many

instructions to address transformation and data manipulation to support the few instructions that do the actual computation [10]. Full vector architecture mitigates these effects by providing a rich set of memory access and data manipulation instructions, and longer vectors to keep functional units busy and reduce overhead [11].

### 2.2.2 Single-chip Vector Processors

The Torrent T0 [12] and VIRAM [6] are single-chip vector microprocessors that support a complete vector architecture and are implemented as custom ASICs. T0 is implemented in full-custom 1.0 µm CMOS technology. The processor contains a custom MIPS scalar unit, and the vector unit connects to the MIPS unit as a co-processor. The vector unit has 16 vector registers, a maximum vector length of 32, and 8 parallel vector lanes. VIRAM is implemented in 0.18 µm technology and runs at 200MHz. It has 32 registers, a 16-entry vector flag register file, and two ALUs replicated over 4 parallel vector lanes. VIRAM has been shown to outperform superscalar and VLIW architectures in the consumer and telecommunications categories of the EEMBC [13] benchmarks by a wide margin [14]. These two vector processors share the most similarity in processor architecture to this work.

RSVP [15] is a reconfigurable streaming vector coprocessor implemented in 0.18 µm technology, and was shown to achieve speedup of 2 to 20 times over its ARM9 host processor alone on a number of embedded kernel benchmarks. Some other vector architectures proposed recently for ASIC implementation are the CODE architecture [16] which is based on multiple vector cores, and the SCALE processor based on the vector-thread architecture [17] that combines multi-thread execution with vector execution. These two architectures were only studied in simulation.

#### 2.2.3 FPGA-based Vector Processors

There have been a few past attempts to implement vector processors in FPGAs. However, most of them targeted only a specific application, or were only prototypes of ASIC implementations.

A vector computer is described in [18] that has pipelined 32-bit floating-point units augmented with custom instructions for solving a set of sparse linear equations. The vector computer has 8 adders and multipliers, supports a vector length of 16, and has a 128-bit data bus that can transfer four 32-bit words. Little additional information is given about the system other than it was mapped to a Xilinx Virtex II FPGA. ProHos [19] is a vector processor for computing higher order statistics. Its core is a pipelined MAC unit with three multipliers and one accumulator. The processor is implemented on the RVC [20] platform consisting of five Xilinx 4000E devices, and runs at 7.5MHz. The SCALE vector processor [17] was prototyped in an FPGA [21], but no specific attempt was made to optimize the architecture or implementation for FPGAs.

Three vector processors that, similar to this work, were specifically designed for FPGAs are described in [22], [23], and [24]. The first vector processor [22] consists of two identical vector processors located on two Xilinx XC2V6000 FPGA chips. Each vector microprocessor runs at 70MHz, and contains a simplified scalar processor with 16 instructions, a vector unit consisting of 8 vector registers, 8 lanes (each containing a 32-bit floating-point unit), and supports a maximum vector length (MVL) of 64. Eight vector instructions are supported: vector load/store, vector indexed load/store, vector-vector and vector-scalar multiplication/addition. However, only matrix multiplication was demonstrated on the system. Although the vector processor presented in this thesis lacks floating-point support, it presents a more complete solution consisting of full scalar unit (Nios II) and a full vector unit (based on VIRAM instructions) that supports over 45 distinct vector instructions plus variations.

The second vector processor [23] was designed for Xilinx Virtex-4 SX and operated at 169MHz. It contains 16 processing lanes of 16-bit and 17 on-chip memory banks connected to a MicroBlaze processor through fast simplex links (FSL). It is not clear how many vector registers were supported. Compared to the MicroBlaze, speedups of 4–10× were demonstrated with four applications (FIR, IIR, matrix multiply, and 8×8 DCT). The processor implementation seems fairly complete.

The third vector processor [24] is a floating point processing unit based on the T0 archi-

tecture, and operated at 189MHz on a Xilinx Virtex II Pro device. It has 16 vector registers of 32 bits and a vector length of 16. Three functional units were implemented: floating-point adder, floating-point multiplier, and vector memory unit that interfaces to a 256-bit memory bus. All three functional units can operate simultaneously, which together with the 8 parallel vector lanes in the datapath, can achieve 3.02 GFLOPS. No control processor was included for non-floating-point or memory instructions, and it is unclear whether addressing modes other than unit-stride access were implemented.

A Softcore Vector Processor is also presented in [25] for biosequence applications. The processor consists of an instruction controller that executes control flow instructions and broadcast vector instructions to an array of 16-bit wide processing elements (PE). Compared to this thesis, it is a more limited implementation with less features and instructions, but like this thesis it also argues for a soft vector processor core.

Many SIMD systems have also been developed for FPGAs. A SIMD system is presented in [26] that is comprised of 2 to 88 processing elements built around DSP multiplier blocks on a Altera Stratix FPGA, and controlled by a central instruction stream. The system utilizes all the DSP blocks of an Altera Stratix EP1S80 FPGA, but only 17% of the logic resources. Only matrix multiplication was illustrated on the system, but the actual implementation of the application was not described. This system demonstrates the tremendous amount of parallelism available on modern FPGAs for performing parallel computations.

### 2.3 Multiprocessor Systems

In contrast to vector processing systems, where everything executes in lock-step, multiprocessor systems have become popular recently as a way to obtain greater performance. In particular, FPGA-based multiprocessors can be composed of multiple soft core<sup>1</sup> processors, or a combi-

<sup>&</sup>lt;sup>1</sup>Soft core processors are described fully in software, usually in HDL, and is synthesized into hardware and programmed into the device with the rest of the user design.

nation of soft and hard core<sup>2</sup> processors. The parallelism in multiprocessor systems can be described as multiple instruction multiple data (MIMD). Each processor in a MIMD multiprocessor system has its own instruction memory and executes its own instruction stream and operates on different data. In contrast, SIMD systems have a single instruction stream that is shared by all processors. For example, vector processing is a type of SIMD system. In the context of soft processor acceleration, the discussion will focus on multiprocessor systems that utilize multiple soft processors on FPGAs.

Most multiprocessor systems that have been implemented in FPGAs are unique as there are not yet any de facto or formal standards. They usually differ in number of processors, interconnect structure, how processors communicate, and how they access memory. However, the communication scheme in multiprocessor systems can generally be categorized into shared memory or message passing, and the memory architecture can be categorized as either centralized or distributed [27].

FPGA-based multiprocessor systems can be very flexible, allowing them to adapt to accelerate heterogeneous workloads that otherwise do not parallelize effectively. Specialized systems with unique architectures can be designed to exploit the characteristics of a particular application for better performance. For example, the multiprocessor system in [28] for LU matrix factorization has a unique architecture that consists of a system controller that connects to a number of processing elements in a star topology, and seven kinds of memory for communicating data and storing instructions. The IPv4 packet forwarding system in [29] has 12 MicroBlaze processors arranged in four parallel pipelines of processors with each stage performing a specific task. Table 2.1 lists a number of FPGA multiprocessor systems found in literature and their features.

The disadvantage of MIMD multiprocessor systems is their complexity. Significant hardware knowledge is needed to design a multiprocessor system, including consideration of issues

<sup>&</sup>lt;sup>2</sup>Hard core processors are implemented directly in transistors in the device, separate from the user design which is programmed into the programmable logic fabric.

| Multiprocessor | Application                | # CPUs | Speedup | Communication   | Memory      |

|----------------|----------------------------|--------|---------|-----------------|-------------|

| CerberO [30]   | Discrete wavelet transform | 4      | 4       | Shared memory   | Centralized |

| Kulmala [31]   | MPEG-4 encoding            | 4      | 1-3     | Shared memory   | Centralized |

| Martina [32]   | Digital signal processing  | 8      | 7–8     | Shared memory   | Centralized |

| Ravindran [29] | IPv4 packet forwarding     | 16     | n/a     | Message-passing | Distributed |

| SoCrates [33]  | General purpose            | 2      | n/a     | Shared memory   | Distributed |

| Wang [28]      | Matrix operations          | 6      | 4       | Shared memory   | Distributed |

Table 2.1: Partial list of FPGA-based multiprocessor systems in literature

such as interconnect, memory architecture, cache coherence and memory consistency protocols. Creating a custom multiprocessor system architecture to tailor to the needs of a particular application can be a daunting task due to the large design space. On the software front, the user will need parallel programming knowledge to use these systems, which is not within the skillset of the average software developer. Specialized multiprocessor systems add further difficulty of writing software to effectively take advantage of the architecture.

### 2.4 Custom-designed Hardware Accelerators

Hardware accelerators are frequently used in conjunction with soft processors to accelrate certain portions of an application. Traditionally these accelerators are designed manually in HDL by a hardware designer, and connect to the processor via an interface specified by the processor vendor. The next two sections describe two different methods of interfacing custom-designed hardware accelerators to a soft processor. The fundamental disadvantage of these accelerators is they require hardware design effort to implement, verify, and test. Each accelerator, in most cases, also performs only one function. Hence for each portion of the application to accelerate, a different hardware accelerator is needed. This adds further time and design effort.

### 2.4.1 Decoupled Co-processor Accelerators

The co-processor accelerator model is akin to the use of floating-point co-processors in early computer systems. These accelerators are decoupled from the main processor in operation.

The processor provides inputs to start the accelerator, then has the option of executing a different part of the program while the accelerator is running, and finally reads results when they are computed. This is the model adopted by the Xilinx MicroBlaze to interface to custom co-processor accelerators. The MicroBlaze interfaces to accelerators through 16 32-bit Fast Simplex Link (FSL) channels, which are unidirectional point-to-point first in first out (FIFO) communication buffers. The MicroBlaze CPU uses blocking or non-blocking reads and writes to access the FSL channels, and can use up to 8 FSL channels for outputs from the CPU, and 8 FSL channels for inputs to the CPU.

Co-processor accelerators have the advantage that they are decoupled from the main CPU core, allowing both the CPU and accelerator to execute concurrently. Adding co-processor accelerators are less likely to negatively impact the performance of the CPU core compared to more tightly-coupled methods due to their decoupled nature. The design tools also tend to have good support for these accelerators, allowing the programmer to interact with them as easily as calling a function, and without having to write parallel programs. As an example, the MicroBlaze FSL provides simple send and receive functions to communicate with multiple accelerators. Co-processor accelerators also have the advantage that they can act as data master and communicate directly to memory. However, it is frequently up to the user to create the interface manually, which is added work.

#### 2.4.2 Custom Instruction Accelerators

An alternate connection scheme interfaces an accelerator as a custom logic block within the processor's datapath, in parallel to the processor's main ALU. This scheme allows an accelerator to fetch operands directly from the processor's register file, and write results back to the processor's register file using the ALU's result bus. These accelerators effectively extend the functionality of the processor's ALU. The Nios II CPU supports this type of accelerator as custom instructions to the processor. To control the custom accelerators, new instructions are added to the processor, mapping to an unused opcode in the Nios II ISA. These instructions

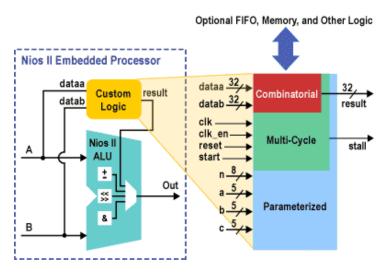

Figure 2.3: Nios II custom instruction accelerators can be combinational, multi-cycle, or contain internal register states (parameterized) (Source: [34])

are then executed directly by the extended ALU of the processor.

The main advantage of custom instructions and other such tightly-coupled accelerators is they can directly access the register file, saving the data movement instructions needed by co-processor accelerators to move data between the processor and accelerator. They are well-integrated into the CPU and development tools due to their exposed nature as CPU instructions, allowing software developers to easily access them at the software level. For example, the Nios II CPU can integrate up to 256 custom instruction accelerators, and they can be accessed in software by calling special functions built into the development tools. These accelerators are also relatively simple to interface to the CPU because the types of custom instructions and their interfaces are already defined in the CPU specification. Nios II defines single-cycle combinational and multi-cycle custom instructions that stall the CPU, and accelerators with additional internal register state (internal flip-flops) programmed by CPU instructions to hold data to process. Figure 2.3 summarizes the Nios II custom instruction formats.

Transferring large amounts of data into and out of these accelerators is, however, a slow process. Due to their intended lightweight nature, custom instruction accelerators generally do not define their own memory interface (although it can be done manually by the designer). Instead, they rely on the processor to perform memory access. In the Nios II case, custom instructions can only read up to two 32-bit operands from the processor register file and write one 32-bit result per instruction, like other Nios II R-type instructions. Another drawback is the accelerators lie on the critical path of the processor ALU. Adding one or more accelerators with complex combinational logic can unnecessarily reduce the maximum frequency of the CPU core, affecting performance of the entire system.

### 2.5 Synthesized Hardware Accelerators

Synthesized hardware accelerators use behavioural synthesis techniques to automatically create hardware accelerators from software. These accelerators and processor systems take on different architectures, and several of them will be described in this section. A common drawback of these approaches is since the tools synthesize hardware from the user's software application, if the user changes hardware-accelerated sections of the software, the register transfer level (RTL) description of the hardware accelerators, and possibly of the entire system, will have to be regenerated and recompiled. This can make it difficult to achieve a targeted clock frequency for the whole design, for example. Synthesis tools also generally create separate hardware accelerators for each accelerated function, with no opportunity for resource sharing between accelerators.

### 2.5.1 C-based Synthesis

Hardware circuits synthesized from software written in the C programming language or variations of it has long been advocated due to the widespread use of C in embedded designs. Although the idea is attractive, in reality there are many difficulties such as identifying and extracting parallelism, scheduling code into properly timed hardware, and analyzing communication patterns and pointer aliasing [35]. Due to these difficulties, C-based synthesis tools

usually do not support full American National Standards Institute (ANSI) C, but only a subset, or employ extensions to the language. For example, floating-point data types are often not supported due to the hardware complexity required. With current automatic synthesis methods, the user also needs to have a good understanding of how to write "C" code that synthesizes efficiently to hardware. Unfortunately, the rules and language subsets often change from one tool to the next.

Given these limitations, C-based synthesis is still a powerful method for creating hardware accelerators, which can be seen from the large number of solutions in this area. The following sections will describe three compilers that support FPGAs: Altera C2H Compiler, Xilinx CHiMPS, and Catapult C. Descriptions of some other C-based synthesis tools can be found in [36].

#### Altera C2H Compiler

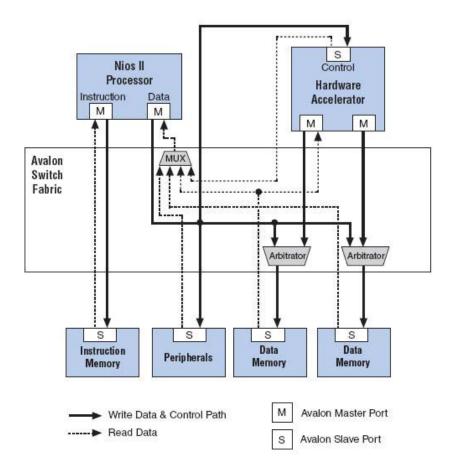

The Altera C2H compiler is a recently released tool that synthesizes a C function into a hardware accelerator for the Nios II soft CPU. The System-on-Programmable-Chip (SOPC) Builder tool in Quartus II automatically connects these accelerators to the Nios II memory system through the Avalon system fabric [37]. The compiler synthesizes pipelined hardware from the C source code using parallel scheduling and direct memory access [38]. Initially, each memory reference in the C language is handled by creating a master port in the accelerator hardware for each memory reference. In theory, this allows the maximum number of concurrent memory accesses. When several master ports connect to the same memory block, the Avalon system fabric creates an arbiter to serialize accesses. As an additional optimization, the C2H compiler will merge several master ports connected to the same memory block by combining the references and scheduling them internally. The ANSI C restrict keyword is used to indicate no aliasing can occur with a pointer to help optimize concurrency. Figure 2.4 shows an example Nios II processor system with C2H accelerators, and the connections between the various components of the system.

The C2H compiler is convenient, and the design flow is simple and well-integrated into the

Figure 2.4: Example Nios II system with C2H accelerators (Source: [38]).

development tools. The pipelined, decoupled co-processors do not have the disadvantages of tightly-coupled custom instruction accelerators, and direct memory access is a powerful feature that further simplifies usage. Despite its ease of use, the performance of the automatically synthesized accelerators are not as good as one might presume. The C2H compiler generates only a single solution in the design space. It has no option to control the amount of loop unrolling to set the performance and resource level of the accelerator. As can be seen from Figure 2.4, if one of the accelerators have to access multiple data elements from a single data memory, it will be forced to serialize the memory accesses, possibly creating a bottleneck in the accelerator. To alleviate this bottleneck, data needs to be partitioned efficiently over multiple memories to reduce overlap. However, this is a step that needs to be done manually by the user, and requires

a good understanding of the hardware system and application. The hardware accelerators also do not have caches, nor do they support cache coherency with the Nios II processor's cache. The user either has to ensure that data does not overlap, or force the processor to flush its cache before transferring execution to the accelerator.

#### CHiMPS Target Language

Compiling HLL Into Massively Pipelined Systems (CHiMPS) is an experimental compiler by Xilinx Labs [39] that compiles high level languages such as C into hardware accelerators that can be implemented on Xilinx FPGAs. The compiler uses the CHiMPS Target Language (CTL), which is a predefined instruction set, as an intermediate language for synthesis, then extracts a dataflow graph from the CTL. This dataflow graph is then implemented in hardware, and pipelined for performance. One additional feature of CHiMPS is it automatically generates caches to cache data inside the FPGA, and supports coherency between multiple cache blocks and multiple FPGAs. Few additional details have been released about CHiMPS, and it is still unclear what further functionality it provides.

#### Catapult Synthesis

Catapult Synthesis [40] by Mentor Graphics synthesizes ANSI C++ into an RTL description that can then be targeted to an ASIC or FPGA. Catapult Synthesis can actually synthesize entire systems without processor cores, and it has been used to design production ASIC and FPGA designs [40]. The tool automatically generates multiple microarchitectures for a given design, allowing the user to explore performance, area, and power tradeoffs. The user can use synthesis directives to specify high-level decisions. A number of main architectural transformations are applied to generate a hardware architecture. Interface synthesis converts the way the C function communicates with the rest of the design, variable and array mapping controls how variables are mapped to registers or memory, loop pipelining allows multiple iterations of a loop to execute in parallel, loop unrolling exploits parallelism across subsequent loop itera-

tions, and scheduling transforms the untimed C code into an architecture with a well-defined cycle-by-cycle behaviour.

The Catapult Synthesis tool allows designers to automate parts of the detailed implementation of a design, while the automatic exploration process allows them to explore tradeoffs in the implementation. However, the user must still specify how data is transferred to and from the accelerator during interface synthesis, and use directives to guide the other phases of compilation. User experience reports [41] emphasize that the user must have a good understanding of the algorithm and implications of different C/C++ constructs to generate good hardware. As Catapult Synthesis is designed to synthesize entire systems, it does not have natural support for connecting to a processor.

#### 2.5.2 Block-based Synthesis

Block-based synthesis describes methods that synthesize hardware from a graphical design environment that allows the user to design systems by graphically connecting functional blocks. This synthesis flow is frequently incorporated into model-based design environments, in which the user creates a high-level executable specification using functional blocksets to define the desired functional behaviour with minimal hardware detail. This executable specification is then used as a reference model while the hardware representation is further specified. The most commonly used such environment is the Mathworks Simulink design environment. This design method allows algorithm designers and hardware designers to work in a common environment, and allows architectural exploration without specifying detailed implementation. Automated synthesis methods from these environments simplify the final implementation phase, bridging the gap between algorithm and hardware designers.

The following subsections will describe four specific tools: Xilinx System Generator for DSP, Altera DSP Builder, Simulink HDL Coder, and Starbridge Viva. Starbridge Viva is the only solution of the four that does not operate within Simulink. Another similar tool that interfaces to Simulink is DSPLogic Reconfigurable Toolbox [42].

#### Xilinx System Generator for DSP & Altera DSP Builder

The Xilinx System Generator for DSP [43] is an add-on that uses Simulink as a front-end to interface to Xilinx IP cores for DSP applications. The Xilinx Blockset includes over 90 common DSP building blocks that interface to Xilinx IP core generators. The System Generator also allows hardware co-simulation of the Simulink model using a Xilinx FPGA-based DSP platform communicating through ethernet or JTAG to accelerate the simulation.

The Altera DSP Builder has mostly the same features as the Xilinx System Generator but is targeted to Altera FPGAs. Pre-designed DSP blocks from the Altera MegaCore functions can be imported into the Simulink design, and the system can be co-simulated using an Altera FPGA through JTAG. The DSP Builder also has blocks for communicating with the Avalon fabric so the accelerators generated by DSP Builder can be instantiated in SOPC Builder systems, and used with the Nios II soft processor.

The advantage of these vendor-specific block libraries is they are highly optimized to the vendor's platform. But since they are specific to a target platform, the Simulink models generated using these flows are no longer platform independent and suffer in portability.

#### Simulink HDL Coder

Simulink HDL Coder [44] generates synthesizable Verilog or VHDL code from Simulink models and Embedded MATLAB [45] code for datapath implementations, as well as from finite-state machines described with the Stateflow tool for control logic implementations. The generated HDL is target independent, bit-exact and cycle-accurate to the Simulink model, and can be implemented on FPGA or ASIC. The tool is a mix of synthesis and a set of supported Simulink models with HDL code. Over 80 Simulink models are supported in version 1.0, with multiple implementations included for some commonly used blocks. The HDL Coder can automatically pipeline Embedded MATLAB function blocks and state machines.

#### Starbridge Viva

Starbridge Viva [46] provides its own drag and drop graphical and object oriented environment for algorithmic development. A parallel algorithm can be modelled by connecting functional objects on a design pallet using transports that represent the data flow. Objects are "polymorphic" and can be used with different data types, data rates, and data precisions allowing reuse and experimentation with design tradeoffs. Built-in objects are, however, relatively primitive constructs like comparators and registers compared to Simulink blocks or DSP blocks in the Xilinx/Altera tools. The software supports a number of reconfigurable high-performance computing (HPC) systems with both FPGA and CPUs, as well as the vendor's own Starbridge Hypercomputers.

#### 2.5.3 Application Specific Instruction Set Processor

Application-specific instruction set processors (ASIPs) have configurable instruction sets that allow the user to extend the processor by adding custom hardware accelerators and instructions. They provide a similar level of configurability as soft processors with custom instructions on FPGAs, but are configured only once before being inserted into an ASIC flow. Adding custom hardware and instructions to ASIPs, however, frequently requires the use of proprietary synthesis languages and compilers. They also share the common disadvantages of synthesized hardware accelerators of requiring separate accelerators for each accelerated function. The Tensilica Xtensa processor will be described in the next section. Another commercial ASIP is the ARC configurable processor [47].

#### Tensilica Xtensa

The Tensilica Xtensa [48] processor is a configurable and extensible processor for ASIC and FPGA design flows. It allows the customer to configure the processor to include or omit features, and add application-specific extensions to the base processor using the Tensilica Instruction Extension language (TIE). These instructions expand the base instruction set of the processor.

TIE is flexible and can be used to describe accelerators that range from multi-cycle pipelined hardware to VLIW, SIMD, and vector architectures. The Tensilica XPRES (Xtensa PRocessor Extension Synthesis) Compiler [49] furthermore creates TIE descriptions from ANSI C/C++ code, allowing direct generation of processor hardware RTL from C/C++ specification. It also allows design space exploration by generating different TIE source files that represent a range of Xtensa processors that trade off performance of the application versus area. However, accelerators generated from TIE are optimized for ASIC and not for FPGA implementation. FPGA support is mainly provided for validation purposes.

#### 2.5.4 Synthesis from Binary Decompilation

Another method of synthesizing hardware accelerators is by binary decompilation techniques that decompile the software binary, and synthesize hardware accelerators from the resulting assembly instructions or description. Two commercial products in this category are Cascade [50] by CriticalBlue and Binachip-FPGA [51]. There are not many details on the performance of Binachip-FPGA, but simulation results reported in [52] of hardware accelerator synthesis from binary decompilation and mapping to a microprocessor plus FPGA system-on-chip are less than impressive. CriticalBlue adopts a different architecture for its accelerators to achieve higher performance, as will be described in the following section.

#### CriticalBlue Cascade

Cascade by CriticalBlue is another tool that automatically synthesizes co-processors to a main processor for SoC, structured ASIC, and Xilinx FPGA platforms. Cascade differs from synthesis-based solutions described in previous sections in that it synthesizes a co-processor by analyzing the compiled object code of an application. The Cascade co-processor has a distinct VLIW processor architecture, different from other dataflow or custom-hardware and loop-pipelining based co-processors such as CHiMPS and the Altera C2H compiler. The co-processor connects to the main CPU via the bus interface of the main processor, and can be

configured as a slave co-processor of the main CPU, or an autonomous streaming co-processor with direct memory access. It is customizable, and the tool automatically performs architecture exploration by generating a range of co-processors with different performance and area. Furthermore, it has options to configure the instruction format and control the amount of instruction decode logic. A single co-processor can also be reused to accelerate multiple non-overlapping portions of an application. The VLIW architecture is, however, not ideal for FPGA implementation, as will be explained in Section 2.6.2.

#### 2.6 Other Soft Processor Architectures

Rather than offloading sections of an application from the soft processor to a hardware accelerator or co-processor to speed up execution, the soft processor itself can be improved to achieve higher performance without the addition of accelerators. More advanced architectures than standard RISC architectures have been explored for soft processors, and several of these will be described in the following sections.

#### 2.6.1 Mitrion Virtual Processor

The Mirion Virtual Processor by Mitrionics [53] is a fine-grained, massively parallel, configurable soft core processor. It is based on a collection of ALU tiles that each perform a different function, and are interconnected by a network. The processor is programmed in the proprietary Mitrion-C programming language, which has C-like syntax and allows the programmer to identify parallelism within the code. The user can partially control resource usage by selecting the level of loop unroll in the application. The compiler and configurator then analyzes the application source code, and generates a configuration of the processor that executes the application. Currently, the processor is supported on Xilinx FPGAs.

Although the processor and tools provide a complete solution to automatically synthesize a system to execute the user application, similar to synthesized hardware accelerators, the processor has to be reconfigured whenever the application changes, due to the code-specific nature of the processor configurator.

#### 2.6.2 VLIW Processors

VLIW architectures have also been used in FPGAs for acceleration. VLIW soft processors like [54] are designed for a specific application, while others like [55–57] are more general purpose. The 4-way VLIW processor described in [56] has four identical, general-purpose functional units, connected to a single, multi-ported, 32 × 32-bit register file. It supports automatically generated custom hardware units that can be placed inside each of the identical ALUs. A similar VLIW processor in architecture is [57], which is configurable and is automatically generated by a configuration tool. It has multiple heterogeneous functional units, but also supports custom hardware units coded in VHDL. The register file is separated into three smaller register files for address, data, and data to custom hardware units. Each of the smaller register files are further separated into even and odd register banks to reduce the number connections.

Another FPGA-based VLIW processor is the VPF [58], which is a simplified version of the EVP [59] ASIC. Each funtional unit in the VLIW architecture is itself a SIMD unit that can processes a number of 16-bit operands, with the SIMD width configurable at compile time. The processor has three functional units: MAC, shuffle, and load/store, and seems relatively complete with 52 instructions. A 200MHz clock frequency was achieved for SIMD width of 4 and 8, and performance degrades significantly past SIMD width of 16, mainly due to the shuffle unit which allows arbitrary permutation of data elements across the SIMD unit.

A model of the Intel Itanium microarchitecture supporting a subset of the Itanium ISA was also prototyped on an FPGA [60].